Логические элементы троичной циклической инверсии:

Правая циклическая инверсия (cycle, rotate up).

Левая циклическая инверсия (inverse cycle, rotate down).

Как уже упоминалось ранее, в троичной логике логические элементы «MIN», «MAX» и троичный инвертор «INV» в отличие от своих двоичных аналогов — «И», «ИЛИ», «НЕ» — не образуют функционально полный логический базис, на основе которого можно реализовать любое, сколь угодно сложное троичное устройство. И причиной этого является некоторое различие функций двоичного и троичного инверторов.

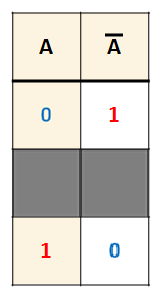

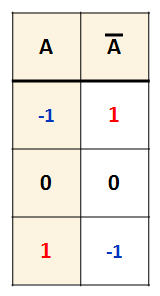

Напомним в сравнении их таблицы истинности, которые уже обсуждались ранее.

|

|

Двоичная инверсия |

Троичная инверсия |

Согласно определению, в двоичной цифровой логике инвертор или элемент «НЕ» — это логический элемент, который реализует логическое отрицание. Он выдает значение, противоположное тому, которое поступило на его вход.

Троичный инвертор фактически выполняет полностью идентичные функции с учетом того, что инверсия состояния лог. «0» («НЕИЗВЕСТНО») и есть сам лог. «0».

Но в силу ограниченности алфавита двоичных функций, двоичный инвертор можно рассматривать и как элемент, неявно увеличивающий или уменьшающий свой аргумент по модулю 2.

Если представить работу двоичного счетного триггера (изображен на рисунке ниже),

то по активному сигналу на тактовом входе C он переписывает по входу D инвертированное значение с инверсного выхода /Q на выход Q. Таким образом в пределах одного разряда осуществляется либо инкремент хранящегося в счетном триггере значения, либо его декремент по модулю 2, поскольку нет никаких сигналов переноса.

Если соединить группу счетных триггеров последовательно так, что выход Q каждого предыдущего соединяется с входом C последующего, получим счетчик на увеличение. Если же вход C последующего счетного триггера соединять с инверсным выходом /Q предыдущего, то счетчик будет работать на вычитание.

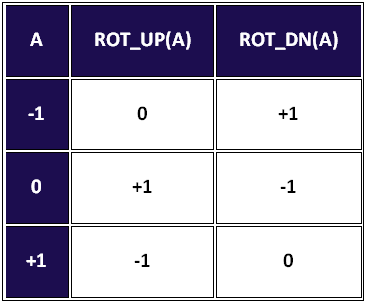

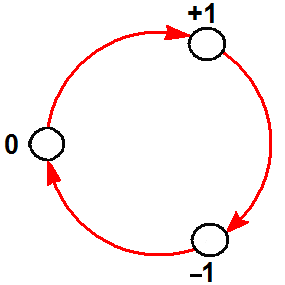

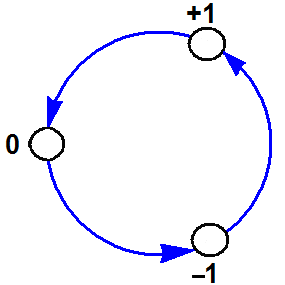

Троичный инвертор же подобным функционалом, свойственным его двоичному аналогу не обладает. В троичной логике функции инкремента и декремента по модулю 3 сильно отличаются от инверсии. Если рассмотреть диаграммы работы троичных счётчиков, работающих как на увеличение, так и на уменьшение (представлены ниже),

становится очевидно, что в троичной логике должны быть функции, осуществляющие операции преобразование входного аргумента следующим образом: лог. «–1» → лог. «0» → лог. «+1» → лог. «–1» и лог. «+1» → лог. «0» → лог. «–1» → лог. «+1». Такие функции, реализующие инкремент и декремент по модулю 3, получили в троичной логике названия, соответственно, правой и левой циклических инверсий, их называют также циклом и обратным циклом или же вращением вверх и вращением вниз. (In ternary logic the modulo 3 increment and decrement functions are called rotate up and rotate down, as well as cycle and inverse cycle. [Standard Ternary Logic]).

Таблицы истинности правой и левой циклической инверсий приведены ниже.

Анализируя их, можно заметить, что правая циклическая инверсия словно вращает столбец входных значений по часовой стрелке вверх, поэтому её называют также rotate up, а левая циклическая инверсия вращает входной столбец против часовой стрелки вниз, соответственно, эту функцию называют rotate down.

|

|

Правая циклическая инверсия |

Левая циклическая инверсия |

Функция левой (или правой) циклической инверсии в совокупности с любой троичной двухвходовой функцией «MIN» (или «MAX») образуют функционально полный логический базис Поста троичной логики. Иными словами, с помощью данных функций и операции суперпозиции можно получить любую другую функцию троичной логики, поскольку любая из функций циклической инверсии способна реализовать операции, свойственные обычной троичной инверсии «INV», в то время как обратное — невозможно.

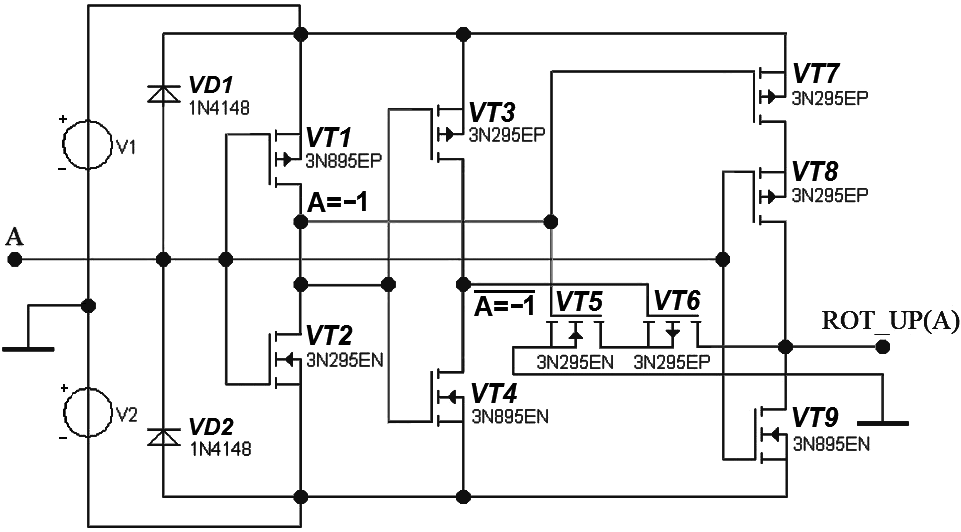

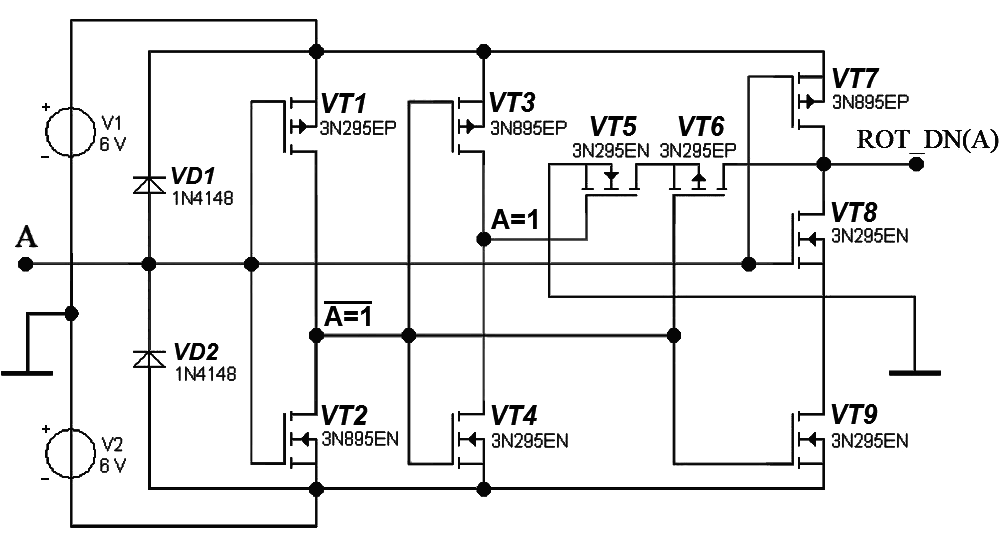

Принципиальная электрическая схема троичного логического элемента правой циклической инверсии, выполненного на основе МОП–транзисторов, представлена на рисунке ниже.

Транзисторы VT1 и VT2 образуют декодер троичного логического состояния лог. «–1». Если на входе A присутствует уровень троичного логического состояния «–1», то на стоках транзисторов формируется логическое состояние «+1», во всех остальных случаях — лог. «–1».

Транзисторы VT3 и VT4 инвертируют этот сигнал, и на их стоках формируется лог. «–1», в том случае, если на входе A присутствует уровень троичного логического состояния «–1», во всех остальных случаях — лог. «+1».

В этом случае выходной сигнал на стоках транзисторов VT1 и VT2 открывает транзистор VT5, а сигнал на стоках транзисторов VT3 и VT4 открывает транзистор VT6. Выходной сигнал на стоках транзисторов VT1 и VT2 одновременно закрывает транзистор VT7. Непосредственно входной сигнал A закрывает транзистор VT9 и открывает транзистор VT8, но он включен последовательно с транзистором VT7, который в этот момент закрыт.

Следовательно, при наличии на входе A уровня троичной логической «–1», на выходе через открытые транзисторы VT5 и VT6 формируется уровень троичного логического «0», и осуществляется преобразование лог. «–1» → лог. «0».

Если же на входе A присутствует уровень троичного логического состояния «0», то на стоках транзисторов VT1 и VT2 формируется логическое состояние «–1», которое закрывает транзистор VT5, и открывает транзистор VT7. Сигнал лог. «+1» на стоках транзисторов VT3 и VT4 закрывает транзистор VT6. Входной сигнал A уровня лог. «0» открывает транзистор VT8, но удерживает закрытым транзистор VT9. Таким образом, через открытые транзисторы VT7 и VT8 на выход поступает потенциал положительной шины питания, и формируется уровень лог. «+1», осуществляя тем самым преобразование лог. «0» → лог. «+1».

В том случае, когда на входе A присутствует уровень троичного логического состояния «+1», на стоках транзисторов VT1 и VT2 по-прежнему формируется логическое состояние «–1», которое закрывает транзистор VT5, и открывает транзистор VT7, а сигнал лог. «+1» на стоках транзисторов VT3 и VT4 закрывает транзистор VT6.

Входной сигнал A уровня лог. «+1» открывает транзистор VT9, но закрывает транзистор VT8. Таким образом, несмотря на то, что транзистор VT7 открыт, через закрытый транзистор VT8 потенциал положительной шины питания на выход не поступает. А открытый транзистор VT9, соединяя выход с потенциалом отрицательной шины питания, формирует уровень лог. «–1», осуществляя тем самым преобразование лог. «+1» → лог. «–1».

Очевидно, что элемент правой циклической инверсии, выполненный по приведенной выше схеме, функционирует в соответствии со своей таблицей истинности.

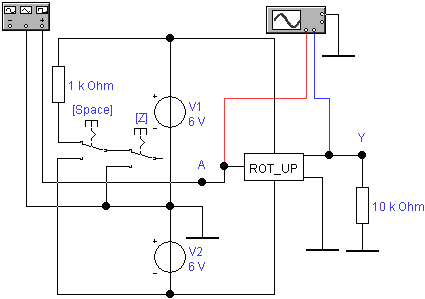

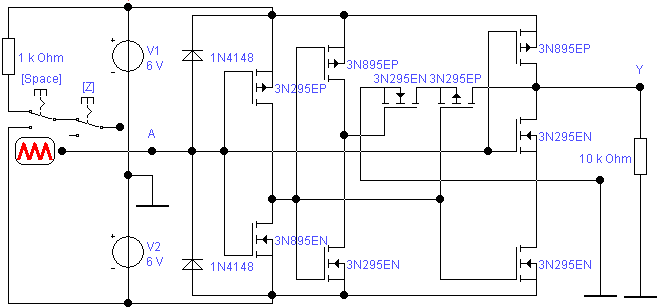

Схема элемента правой циклической инверсии была исследована в программе схемотехнического моделирования на модели, представленной ниже.

Во входных цепях предусмотрена возможность коммутировать логические сигналы вручную с помощью двух переключателей, управляемых клавишами [Space] и [Z]. Резистор номиналом 1 кОм формирует сигнал лог. «1», переключатели позволяют подать на вход A потенциалы лог. «0» и лог. «–1».

Диоды, подключенные между шинами питания и входом A, выполняют защитную функцию, а также вносят во входной импеданс устройства свою емкостную составляющую при моделировании схемы.

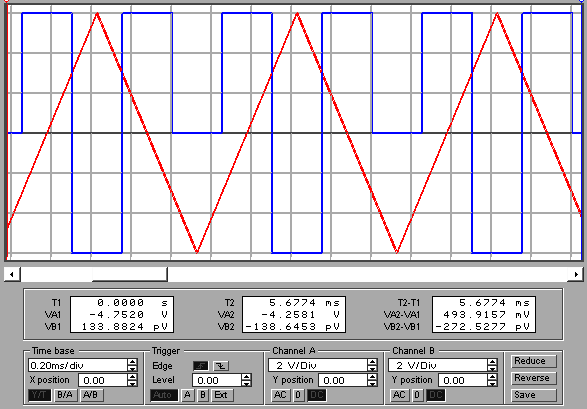

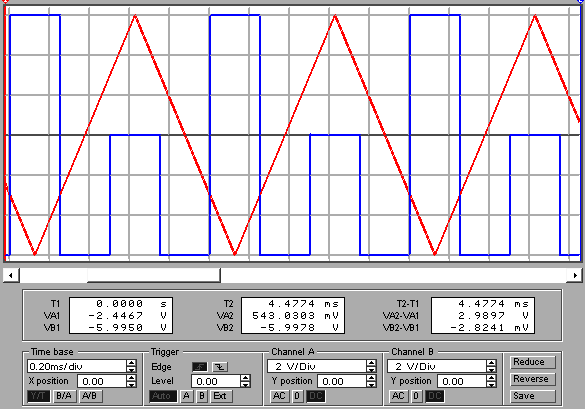

Ниже приведены осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A устройства, и выходного сигнала (синий цвет) элемента правой циклической инверсии.

Очевидно, что выходной сигнал Y (синий цвет) по отношению к входному пилообразному сигналу (красный цвет) изменяется по следующей закономерности: лог. «–1» → лог. «0», лог. «0» → лог. «+1», лог. «+1» → лог. «–1», что полностью соответствует логике работы троичного элемента правой циклической инверсии.

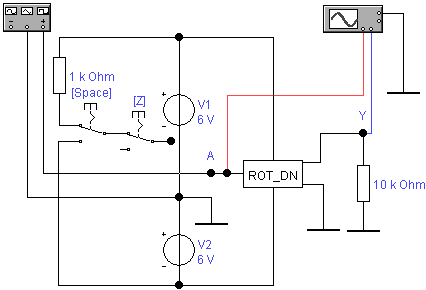

Модель была оформлена в виде отдельного функционального модуля «ROT_UP» (ROTate UP — вращение вверх), который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Рассмотрим далее приведённую ниже принципиальную электрическую схему троичного логического элемента левой циклической инверсии, выполненного на основе МОП–транзисторов.

Транзисторы VT1 и VT2 в этой схеме образуют декодер троичного логического состояния лог. «+1». Если на входе A присутствует уровень троичного логического состояния «+1», то на стоках транзисторов формируется логическое состояние «–1», во всех остальных случаях — лог. «+1».

Транзисторы VT3 и VT4 образуют инвертор этого сигнала, и на их стоках формируется лог. «+1», в том случае, если на входе A присутствует уровень троичного логического состояния «+1», во всех остальных случаях — лог. «–1».

В этом случае выходной сигнал лог. «–1»на стоках транзисторов VT1 и VT2 открывает транзистор VT6 и закрывает транзистор VT9. Сигнал на стоках транзисторов VT3 и VT4 открывает транзистор VT5, а непосредственно входной сигнал A закрывает транзистор VT7 и открывает транзистор VT8, но он включен последовательно с транзистором VT7, который в этот момент закрыт.

Следовательно, при наличии на входе A уровня троичной логической «+1», на выходе через открытые транзисторы VT5 и VT6 формируется уровень троичного логического «0», и осуществляется преобразование лог. «+1» → лог. «0».

Если же на входе A присутствует уровень троичного логического состояния «0», то на стоках транзисторов VT1 и VT2 формируется логическое состояние «+1», которое закрывает транзистор VT5, и открывает транзистор VT9. Сигнал лог. «–1» на стоках транзисторов VT3 и VT4 закрывает транзистор VT6. Входной сигнал A уровня лог. «0» открывает транзистор VT7, но закрывает транзистор VT8. Таким образом, через соединенные последовательно транзисторы VT7 и VT8 потенциал положительной шины питания на выход не поступает. Через открытый транзистор VT9 на выход поступает потенциал отрицательной шины питания, в результате чего формируется уровень лог. «–1», и осуществляется преобразование лог. «0» → лог. «–1».

В том случае, когда на входе A присутствует уровень троичного логического состояния «–1», на стоках транзисторов VT1 и VT2 по-прежнему формируется логическое состояние «–1», которое закрывает транзистор VT5, и открывает транзистор VT7, а сигнал лог. «+1» на стоках транзисторов VT3 и VT4 закрывает транзистор VT6.

Входной сигнал A уровня лог. «–1» закрывает транзистор VT9, но открывает транзистор VT8. Таким образом, через транзисторы VT7 и VT8, включенные последовательно, на выход поступает потенциал положительной шины питания, и формируется уровень лог. «+1». Таким образом осуществляется преобразование лог. «–1» → лог. «+1».

Очевидно, что элемент левой циклической инверсии, выполненный по приведенной выше схеме, функционирует в соответствии со своей таблицей истинности.

На модели, представленной ниже, в программе схемотехнического моделирования была исследована схема элемента левой циклической инверсии.

Диоды, подключенные между шинами питания и входом A, выполняют защитную функцию, а также вносят во входной импеданс устройства свою емкостную составляющую при моделировании схемы.

Во входных цепях также предусмотрена возможность коммутировать логические сигналы вручную с помощью двух переключателей, управляемых клавишами [Space] и [Z]. Резистор номиналом 1 кОм формирует сигнал лог. «1», переключатели позволяют подать на вход A потенциалы лог. «0» и лог. «–1».

Осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A устройства, и выходного сигнала (синий цвет) элемента левой циклической инверсии приведены на рисунке ниже.

Осциллограммы подтверждают, что выходной сигнал Y (синий цвет) по отношению к входному пилообразному сигналу (красный цвет) изменяется по следующей закономерности: лог. «+1» → лог. «0», лог. «0» → лог. «–1», лог. «–1» → лог. «+1», что полностью соответствует логике работы троичного элемента левой циклической инверсии.

Модель была оформлена в виде отдельного функционального модуля «ROT_DN» (ROTate DowN — вращение вниз), который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Элементы левой и правой циклической инверсии практически незаменимы при построении схем троичных асинхронных счетчиков.

Но сердцем любого современного процессора, безусловно, является сумматор. И важной составной частью полного троичного сумматора является сумматор по модулю три, устройству которого посвящена следующая часть.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download