Троичные асинхронные счетчики и регистры

Двоичный счетчик в общем случае — это цифровое устройство, которое преобразует число входных импульсов в двоичный код, соответствующий числу поступивших импульсов.

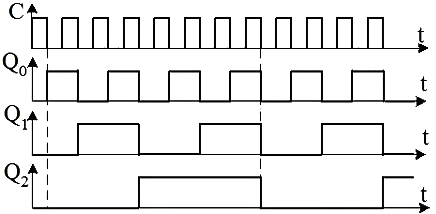

Асинхронные счетчики строятся на основе простой цепочки счетных триггеров, включенных последовательно друг за другом, как это показано на рисунке ниже.

Выходной сигнал каждого триггера служит входным сигналом для следующего триггера. Поэтому все разряды (выходы) асинхронного счетчика переключаются последовательно (отсюда название — последовательные счетчики), один за другим, начиная с младшего и заканчивая старшим. Несмотря на то, что сам по себе счетный триггер является синхронным устройством, каждый следующий разряд счетчика переключается с задержкой относительно предыдущего, то есть, вообще говоря, асинхронно и не одновременно как с входным сигналом, так и с другими разрядами.

Счетчик, схема которого представлена на рисунке выше, является суммирующим. Иначе говоря, с приходом каждого последующего входного импульса значение на его выходах увеличивается на единицу.

Если вход каждого последующего счетного триггера соединить с инверсным выходом предыдущего, то результирующее устройство будет работать как вычитающий счетчик.

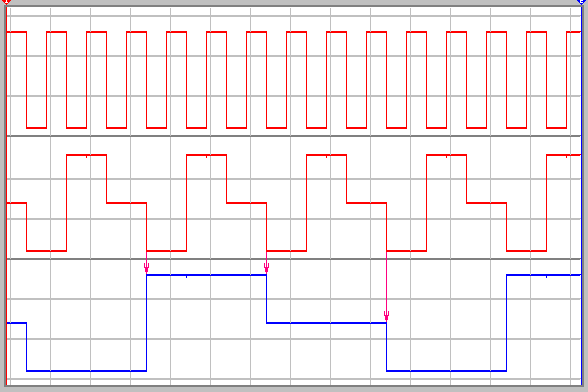

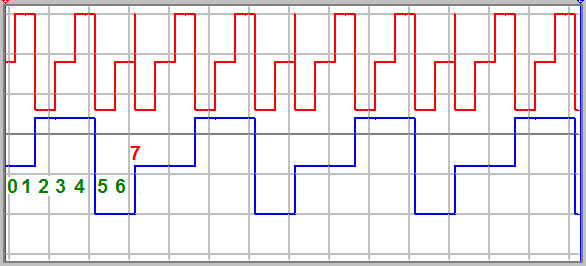

Ниже представлены осциллограммы работы суммирующего асинхронного двоичного счетчика (справа) и вычитающего — слева.

|

|

Следует подчеркнуть, что триггеры двоичных счётчиков при включении устанавливаются обычно в произвольное состояние, поэтому приведенные выше осциллограммы на практике получаются либо спустя некоторый интервал времени от произвольного начала счета, либо благодаря введению в структуру двоичных триггеров специальных асинхронных цепей предустановки.

По аналогии можно постулировать, что троичный счетчик — это цифровое устройство, которое преобразует число входных импульсов в троичный код, соответствующий числу поступивших импульсов. И, соответственно, асинхронный троичный счетчик можно выполнить на основе простой цепочки троичных счетных триггеров, включенных последовательно друг за другом.

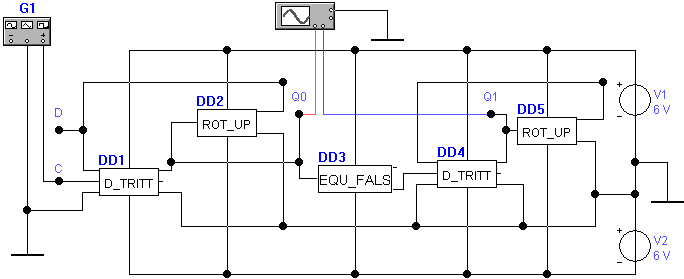

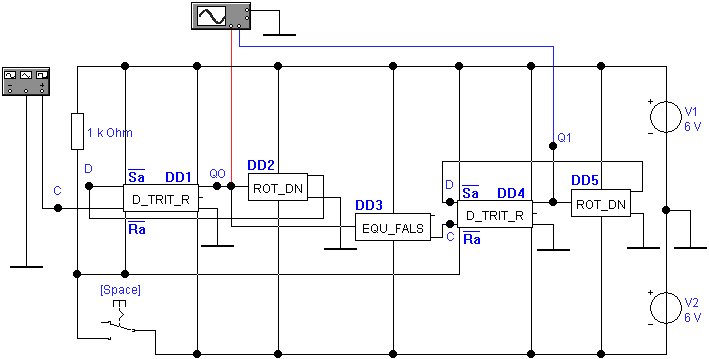

На рисунке ниже представлен троичный двухразрядный асинхронный счетчик, реализованный в программе схемотехнического моделирования путём каскадирования двух троичных счетных триггеров.

Элементы DD1 и DD2, соответственно, троичный динамический D–триггер, работающий по спаду тактового сигнала, и элемент правой циклической инверсии образуют первый троичный счетный триггер, а элементы DD4 и DD5 — второй.

Элемент DD3 — декодер отрицательного троичного уровня — обеспечивает динамическому D–триттеру крутой перепад управляющего сигнала, предотвращающий возможные сбои при прохождении уровня «0».

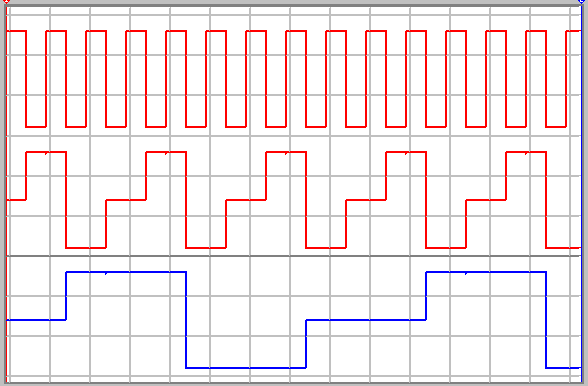

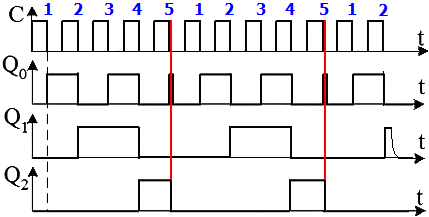

Осциллограммы сигналов, измеренные при тестировании троичного двухразрядного счетчика, приведены на рисунке ниже.

Осциллограммы демонстрируют бессбойный счет на увеличение по срезам управляющих сигналов и подтверждают работоспособность троичного двухразрядного счетчика.

Следует отметить, что в отличие от двоичного счетчика, триггеры троичного счетчика устанавливаются в лог. «0» по умолчанию, без специальных цепей начальной установки.

Также необходимо подчеркнуть, что двухразрядный троичный счётчик способен подсчитать 9 входных импульсов до переполнения, в то время как трёхразрядный двоичный счетчик — всего лишь 8.

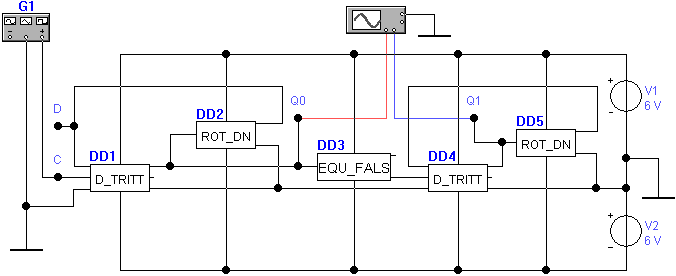

Троичный двухразрядный асинхронный вычитающий счетчик, реализованный в программе схемотехнического моделирования путём каскадирования двух троичных счетных триггеров, представлен на рисунке ниже.

Элементы DD1 и DD2, соответственно, — троичный динамический D–триггер, работающий по спаду тактового сигнала, и элемент левой циклической инверсии образуют первый троичный счетный триггер, работающий в режиме декремента, а элементы DD4 и DD5 — второй.

Элемент DD3 — декодер отрицательного троичного уровня — обеспечивает динамическому D–триттеру крутой перепад управляющего сигнала, предотвращающий возможные сбои при прохождении уровня «0».

На рисунке ниже приведены осциллограммы сигналов, измеренные при тестировании троичного двухразрядного вычитающего счетчика

Очевидно, что модель троичного двухразрядного вычитающего счетчика демонстрируют бессбойный счет на уменьшение по срезам управляющих сигналов, что подтверждает её практическую работоспособность.

Необходимо подчеркнуть, что в данном случае элемент DD3 — декодер отрицательного троичного уровня — играет более важную роль, поскольку обеспечивает динамическому D–триттеру крутой перепад управляющего сигнала, при коротком его срезе на переходе «0» → «–1» (показано на осциллограмме стрелками).

Двоичные N–разрядные счетчики позволяют осуществлять деление частоты следования сигналов счета с коэффициентом пересчета, равным 2N. На их основе могут быть построены делители частоты и счетчики с произвольным коэффициентом пересчета.

Для построения пересчетных схем с произвольным коэффициентом деления частоты могут использоваться Т–триггеры, имеющие дополнительные асинхронные входы установки триггера в состояние логической «1» (вход Set) или установки в состояние логического «0» (вход Reset).

Дополнительные асинхронные входы установки двоичного синхронного триггера могут быть введены в его схему следующим образом:

То есть, основа схемы — асинхронный RS–триггер выполняется на логических элементах «3И-НЕ», дополнительные выводы которых послужат в качестве асинхронных входов предустановки или сброса синхронного триггера. При этом асинхронные входы имеют преимущество над синхронными, поскольку воздействуют непосредственно на асинхронный RS–триггер.

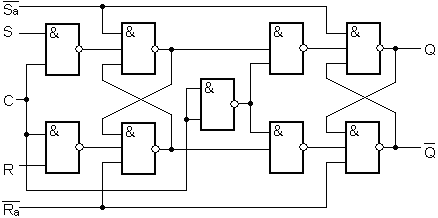

Синхронный RS–триттер также можно модифицировать подобным образом и ввести дополнительные асинхронные входы предустановки, как это показано на рисунке ниже.

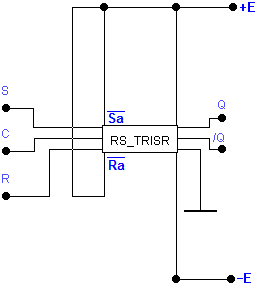

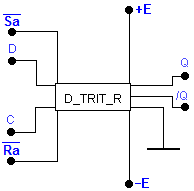

И если оформить этот узел в виде отдельного функционального модуля, как показано на рисунке ниже.

То можно реализовать на его основе троичные двухступенчатые D–триттеры с функцией предустановки или сброса.

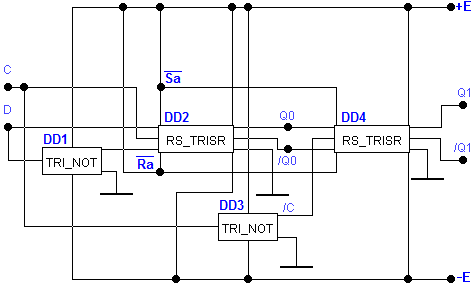

Из функциональных модулей которых, представленных на рисунке ниже

можно реализовать троичные счётчики с функцией предустановки или сброса.

Модель такого двухразрядного суммирующего счётчика показана на рисунке ниже.

Нажатием кнопки [Space] можно асинхронно в любой момент сбросить оба триттера счётчика в состояние «–1». Входы установки в состояние «+1» не используются, и подключены к высокому потенциалу шины питания.

На осциллограмме ниже цветной стрелкой обозначен момент, во время которого поступил асинхронный сигнал сброса по нажатию кнопки [Space].

После чего счётчик продолжил счёт по тактовым импульсам из положения установленного асинхронно.

Вполне естественно, что ввести дополнительные асинхронные входы сброса и предустановки можно также и в вычитающий счётчик, как это показано на рисунке ниже.

Если использовать дополнительные асинхронные входы счетного триггера, то существует возможность с помощью дополнительной логики организовать счётчик с заданным произвольным коэффициентом пересчёта, меньшим максимального числа счета отдельного счётчика. Сигнал окончания счета формируется как логическое произведение единичных сигналов с выходов тех разрядов счетчика, которые соответствуют единицам в двоичном числе равном К–1, где К – полный коэффициент пересчета.

Проще говоря, с помощью логического элемента «И-НЕ» с необходимым числом входов отслеживается уникальный код числа на выходах счетчика, по достижению которого этот логический элемент подаст сигнал сброса на все счетные триггеры одновременно.

В ряде случаев логический элемент «И-НЕ» входит непосредственно в состав счётчика и используется для формирования управляющего сигнала после поступления заданного числа счетных импульсов.

На рисунке ниже логический элемент «И-НЕ» отслеживает комбинацию на выходах — 101, то есть, осуществляет сброс счётчика по приходу пятого импульса, тогда как трёхразрядный двоичный счётчик способен считать до К=8.

Комбинация 101 уникальна, и до её появления такого совпадения единичных сигналов не встречается, что подтверждает осциллограмма счета, приведенная на рисунке ниже.

Осциллограмма показывает, что по спаду пятого тактового импульса в момент сброса появляется помеха типа «иголка» по выходу Q0. Помехи и сбои могут появиться из-за того, что триггеры асинхронных счетчиков срабатывают с задержкой распространения, что может проявляться в мгновенных ложных состояниях счётчика.

Тем не менее, подобный способ организации счётчика с заданным произвольным коэффициентом пересчёта вполне применим и в схемотехнике троичных устройств. Ситуация осложняется лишь тем, что при трёхуровневом сигнале для отслеживания необходимой комбинации на выходах троичного счётчика придётся задействовать декодеры логических уровней, по совпадению единичных уровней на выходах которых с помощью логического элемента отслеживать необходимую комбинацию для подачи сигнала сброса или предустановки.

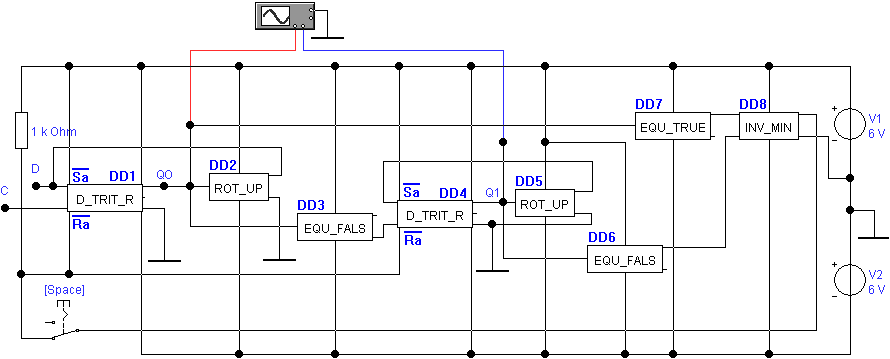

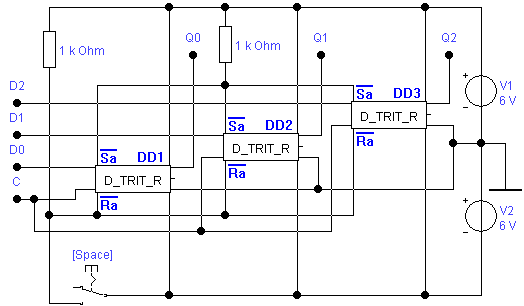

На рисунке ниже представлена модель троичного двухразрядного счётчика на увеличение, сброс которого осуществляется по комбинации Q0 = «+1», Q1 = «–1».

Элементы DD1 и DD2 — троичный динамический D–триггер, работающий по спаду тактового сигнала, и элемент правой циклической инверсии образуют первый троичный счетный триггер, работающий в режиме инкремента, а элементы DD4 и DD5 — второй.

Элемент DD3 — декодер отрицательного троичного уровня — обеспечивает динамическому D–триттеру DD4 крутой перепад управляющего сигнала, предотвращающий возможные сбои при прохождении уровня «0».

Оба динамических троичных D–триггера DD1 и DD4 имеют асинхронные входы предустановки /Sa и сброса /Ra низким уровнем «–1», причем оба входа предустановки /Sa подключены к положительной шине источника питания, в силу чего не оказывают влияния на работу устройства. Входы же сброса /Ra обоих триттеров объединены и отвечают за перевод триттеров в состояние «–1».

Элемент DD7 — декодер положительного троичного уровня, подключенный на выходе Q0 счетчика, и элемент DD6 — декодер отрицательного троичного уровня, подключенный на выходе Q1 счетчика, отслеживают уровни Q0 = «+1», Q1 = «–1», соответственно. По совпадению этих сигналов элемент DD8, избирательно реагирующий на совпадение уровней лог. «+1», подаёт сигнал лог. «–1» на входы сброса /Ra троичных D–триггеров DD1 и DD4, переводя их выходы в состояние Q0 = «–1», Q1 = «–1». Этим он ликвидирует ситуацию сброса по совпадению уровней Q0 = «+1», Q1 = «–1», и разрешает счет по поступлению тактовых импульсов на вход C.

Нажатием кнопки [Space] можно отключить механизм сброса и пронаблюдать, как отличаются осциллограммы работы устройства со сбросом по достижению заданного значения и без него.

Ниже представлены осциллограммы работы двухразрядного троичного суммирующего счетчика с опцией сброса по комбинации на выходах Q0 = «+1», Q1 = «–1».

Согласно приведенным выше осциллограммам, сброс счётчика осуществляется по числу 7 на его выходах, после чего вновь начинается счет по поступлению тактовых импульсов на вход C.

Таким образом, продемонстрирована принципиальная возможность создания троичных счетчиков с заданным произвольным коэффициентом пересчёта в пределах максимального коэффициента пересчёта отдельного троичного счетчика.

Важным элементом построения больших синхронных цифровых систем являются регистры.

Регистр — устройство для записи, хранения и считывания n–разрядных двоичных данных и выполнения других операций над ними.

Соответственно, троичные регистры — устройство для записи, хранения и считывания n–разрядных троичных данных и выполнения других операций над ними.

Регистр по определению представляет собой упорядоченный набор триггеров, обычно D–триггеров, число которых соответствует числу разрядов в слове.

Поскольку динамические D–триггеры с асинхронными входами предустановки или сброса есть в нашем наборе троичных устройств, нетрудно организовать на их основе, к примеру, параллельный регистр.

Схема трёхразрядного троичного параллельного регистра с записью по срезу входного тактового импульса, и с асинхронными входами предустановки или сброса представлена на рисунке ниже.

Элементы DD1, DD2, DD3 — троичные динамические D–триггеры, работающие по спаду тактового сигнала. Тактовые входы D–триггеров объединены и образуют единый вход синхронизации C. Входы и выходы триггеров образуют входы и выходы троичного параллельного трёхразрядного регистра D0, D1, D2 и Q0, Q1, Q2, соответственно.

Все три динамических троичных D–триггера DD1, DD2, DD3 имеют асинхронные входы предустановки /Sa и сброса /Ra низким уровнем «–1», причем их входы предустановки /Sa объединены и подключены к положительной шине источника питания через резистор номиналом 1 кОм, в силу чего они не оказывают влияния на работу устройства. Входы же сброса /Ra триттеров также объединены, подключены к положительной шине источника питания через резистор номиналом 1 кОм, и отвечают за перевод триттеров в состояние «–1».

Нажатием кнопки [Space] можно при необходимости сбросить все триттеры троичного параллельного трёхразрядного регистра в состояние «–1».

Существует также возможность установить триттеры троичного параллельного трёхразрядного регистра в состояние «+1», если подключить аналогичную кнопку к объединенным вместе входам предустановки /Sa.

На вход D0 трёхразрядного троичного параллельного регистра подавался трёхуровневый сигнал, сформированный троичным инвертором из синусоидального сигнала отдельного источника частотой 500 Гц и амплитудой 5 В.

На вход D1 подавался трёхуровневый сигнал, сформированный троичным элементом правой циклической инверсии из выходного сигнала троичного инвертора.

На вход D2 подавался трёхуровневый сигнал, сформированный троичным элементом правой циклической инверсии из сигнала с входа D1.

Такой способ формирования входных сигналов был применен с той целью, чтобы сигналы на входах D0, D1, D2 различались по форме, но узел их формирования не был бы столь сложным, как, к примеру, троичный счетчик, и не замедлял бы численный эксперимент.

На вход C подавался импульсный синхросигнал от генератора импульсов частотой 3 кГц, амплитудой 12 В и скважностью 50. Частоты синхросигнала и сигнала данных были выбраны в соотношении 6 : 1, чтобы активный срез синхроимпульсов приходился на все части сформированных трёхуровневых сигналов.

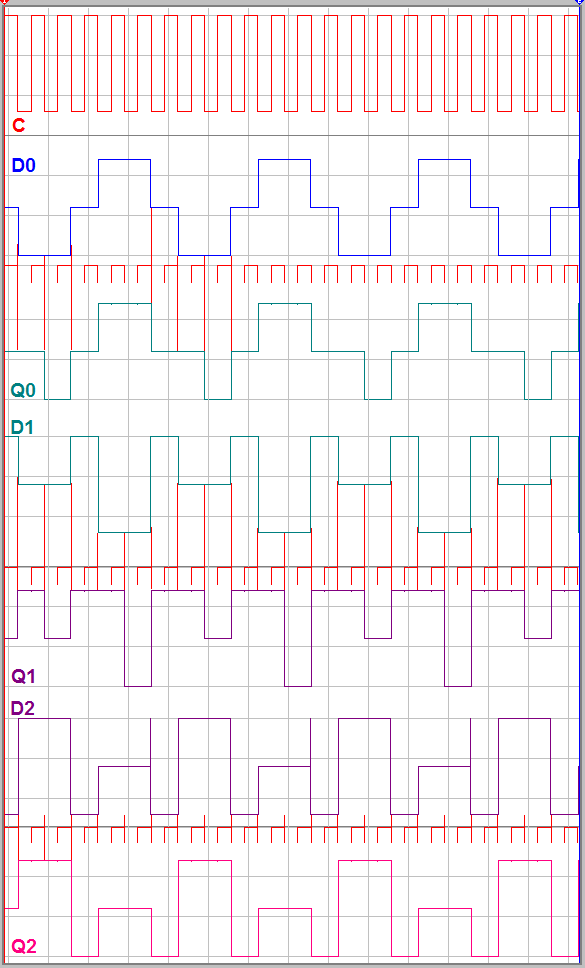

Осциллограммы входных и выходных сигналов трёхразрядного троичного параллельного регистра приведены на рисунке ниже.

Осциллограммы

Очевидно, что троичный трёхразрядный параллельный регистр по срезу стробирующего импульса на входе C успешно фиксирует на своих выходах Q0, Q1, Q2 трёхуровневые входные сигналы с входов D0, D1, D2.

Сдвиговый регистр или регистр сдвига по определению — тип цифровой схемы, использующей каскад D–триггеров, где выход одного триггера соединен с входом следующего. Они совместно используют один тактовый сигнал, который приводит к последовательному перемещению (сдвигу) данных вдоль цепочки триггеров.

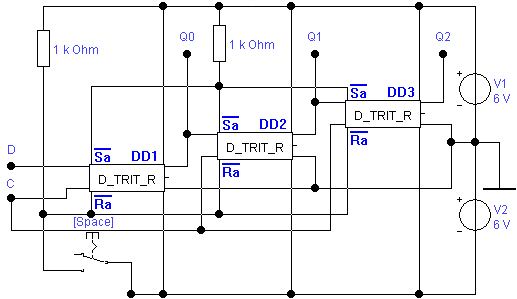

Схема троичного трёхразрядного регистра сдвига с записью и сдвигом по срезу входного тактового импульса, и с асинхронными входами предустановки или сброса представлена на рисунке ниже.

Элементы DD1, DD2, DD3 — троичные динамические D–триггеры, работающие по спаду тактового сигнала. Тактовые входы D–триггеров объединены и образуют единый вход синхронизации C. Вход D каждого последующего триггера соединён с выходом предыдущего. Вход D триггера DD1 является входом всего троичного трёхразрядного регистра сдвига.

Все три динамических троичных D–триггера DD1, DD2, DD3 имеют асинхронные входы предустановки /Sa и сброса /Ra низким уровнем «–1», причем их входы предустановки /Sa объединены и подключены к положительной шине источника питания через резистор номиналом 1 кОм, в силу чего они не оказывают влияния на работу устройства. Входы же сброса /Ra триттеров также объединены, подключены к положительной шине источника питания через резистор номиналом 1 кОм, и отвечают за перевод триттеров в состояние «–1».

Нажатием кнопки [Space] можно при необходимости сбросить все триттеры троичного регистра сдвига в состояние «–1».

Существует также возможность установить триттеры троичного трёхразрядного регистра сдвига в состояние «+1», если подключить аналогичную кнопку к объединенным вместе входам предустановки /Sa.

На вход D троичного трёхразрядного регистра сдвига подавался трёхуровневый сигнал, сформированный троичным инвертором из синусоидального сигнала отдельного источника частотой 500 Гц и амплитудой 5 В.

На вход C подавался импульсный синхросигнал от генератора импульсов частотой 3 кГц, амплитудой 12 В и скважностью 50. Частоты синхросигнала и сигнала данных были выбраны в соотношении 6 : 1, чтобы активный срез синхроимпульсов приходился на все части сформированных трёхуровневых сигналов.

Осциллограммы входных и выходных сигналов трёхразрядного троичного параллельного регистра приведены на рисунке ниже.

Осциллограммы

Очевидно, что троичный трёхразрядный регистр сдвига по срезу стробирующего импульса на входе C успешно фиксирует на своих выходах Q0, Q1, Q2 трёхуровневый входной сигнал с входа D с задержкой для каждого следующего выхода, равной периоду повторения синхронизирующих импульсов.

Таким образом, продемонстрирована принципиальная возможность создания троичных регистров параллельного и сдвигового с асинхронными входами предустановки и сброса.

Представленные в этом разделе троичные счётчики и регистры обрабатывают информацию в троичном позиционном коде, где каждому разряду соответствует степень числа 3.

Интерпретация троичного позиционного кода в троичных цифровых системах возложена на преобразователи кодов — дешифраторы и шифраторы.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download