Двоичный КМОП–инвертор

(двоичное логическое отрицание, «НЕ»)

Прежде чем перейти к обсуждению логического элемента, реализующего функцию троичного отрицания (троичной инверсии) рассмотрим подробно схемотехнику двоичного логического инвертора, что позволит в дальнейшем использовать его схемотехнические решения по индукции.

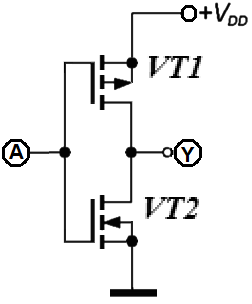

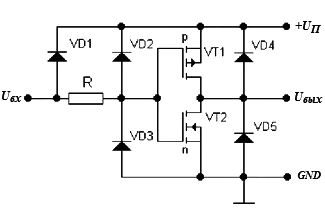

Упрощенная схема двоичного логического инвертора на основе КМОП–транзисторов, корректно отражающая, тем не менее, принципы его работы, представлена на рисунке ниже.

Инвертор состоит из двух полевых МОП–транзисторов с индуцированным каналом нормально закрытого типа, работающих в режиме обогащения: с каналом P-типа (верхний) и каналом N-типа (нижний).

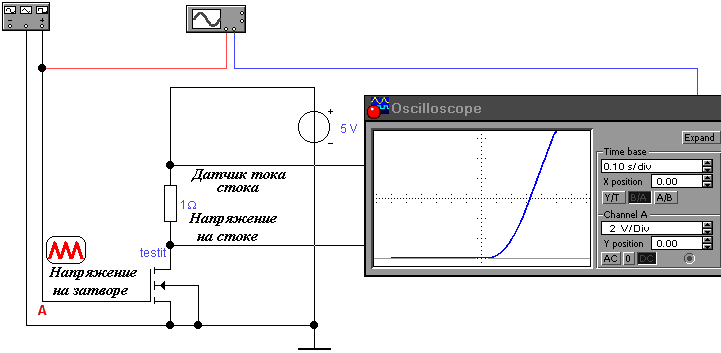

Сток–затворная характеристика нормально закрытого МОП–транзистора с каналом N-типа, работающего в режиме обогащения, представлена на рисунке ниже.

При подаче на затвор нормально закрытого МОП–транзистора пилообразного напряжения в диапазоне от 0 В до +VDD (до +5 В на рисунке выше) ток стока, начиная с некого значения порогового напряжения VПОР, начинает увеличиваться, причем зависимость его от напряжения на затворе VЗ близка к линейной.

Сток–затворная характеристика нормально закрытого МОП–транзистора с каналом P-типа, работающего в режиме обогащения, представлена на следующем рисунке.

Транзистор подключен истоком и подложкой к шине питания +VDD (+5 В на рисунке выше), низкоомный резистор, являющийся датчиком тока стока, подключен между выводом стока и общим проводом — шиной GND. Фактически в обоих случаях на осциллограф подаётся напряжение ICR, пропорциональное току стока IC, поскольку номинал резистора R = 1 Ом. При подаче на затвор нормально закрытого МОП–транзистора с каналом P-типа пилообразного напряжения в диапазоне от +VDD до 0 В ток стока, начиная с некого значения порогового напряжения VПОР, начинает увеличиваться, причем зависимость его от напряжения на затворе VЗ также близка к линейной.

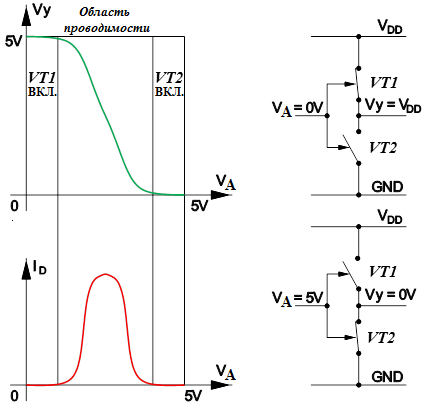

Пороговое напряжение VПОР, МОП–транзисторов в популярных сериях логических микросхем составляет примерно 1.6 В При соединении двух нормально закрытых комплементарных МОП–транзисторов с каналами N- и P-типа по схеме инвертора, наблюдается следующая картина.

При подаче на вход A инвертора (соединённые вместе затворы КМОП–транзисторов) пилообразного напряжения VA в диапазоне от 0 В до +5 В, КМОП–транзистор VT1 полностью открыт, поскольку напряжение на его затворе относительно истока составляет –5 В, что значительно превышает его пороговое напряжение VПОР1. КМОП–транзистор VT2 в этот момент полностью закрыт, поскольку напряжение на его затворе относительно истока составляет 0 В, что значительно меньше его порогового напряжения VПОР2. Таким образом, КМОП–транзистор VT1 в этот момент представляет собой замкнутый ключ, который соединяет шину источника питания VDD с выходом Y. Следовательно, на выходе Y. удерживается высокий потенциал напряжения, благодаря низкому сопротивлению канала транзистора VT1.

При дальнейшем увеличении пилообразного напряжения на входе A инвертора, ток стока IC1 КМОП–транзистора VT1 начинает уменьшаться, поскольку уменьшается напряжение на его затворе относительно истока. При превышении входным сигналом порогового напряжения VПОР2 КМОП–транзистора VT2, он открывается и его канал начинает проводить ток. В диапазоне входного напряжения от VПОР2 до VПОР1 через транзисторы VT1 и VT2 протекает сквозной ток и этот участок принято условно называть «область проводимости». В этой области КМОП–инвертор работает как инвертирующий усилитель с весьма высоким коэффициентом передачи. Поэтому на данном участке он неустойчив, и флуктуации входного напряжения могут привести к хаотичному открыванию и закрыванию транзисторов VT1 и VT2.

При достижении входным сигналом порогового напряжения VПОР1 КМОП–транзистора VT1, он закрывается, а ток транзистора VT2 достигает максимального значения при входном напряжении, равном +VDD.

Таким образом, КМОП–транзистор VT1 в этот момент представляет собой разомкнутый ключ, а транзистор VT2 — замкнутый ключ, который соединяет шину питания GND с выходом Y. При этом на выходе Y. удерживается низкий потенциал напряжения, близкий к 0 В, благодаря низкому сопротивлению канала транзистора VT2.

При уменьшении пилообразного напряжения на входе A инвертора от +VDD до 0 В, процессы происходят в обратном порядке: транзистор VT1 открывается входным напряжением при превышении порогового напряжения VПОР1, а транзистор VT2 — закрывается входным сигналом, когда последний становится меньше порогового напряжения VПОР2.

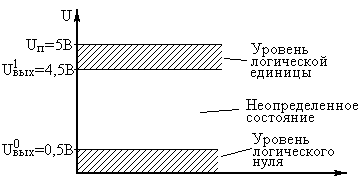

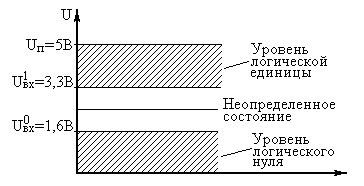

Логические уровни КМОП–микросхем существенно отличаются от логических уровней ТТЛ микросхем. При отсутствии тока нагрузки по выходу Y напряжение на выходе КМОП–микросхемы совпадает с напряжением питания +VDD (логический уровень «1») или с потенциалом общего провода GND (логический уровень «0»). При увеличении тока нагрузки напряжение логической единицы может уменьшается на 2,8 В от напряжения питания (при VDD = +15 В). Допустимый уровень напряжения на выходе цифровой КМОП микросхемы (серия микросхем К561) при напряжении питания VDD = +5 В показан на рисунке ниже.

Разброс уровней напряжение на входе цифровой КМОП–микросхемы по сравнению с уровнями напряжения на выходе обычно допускается в больших пределах. Для КМОП–микросхем существует 30% запас. Границы уровней логического нуля и единицы для КМОП–микросхем при напряжении питания VDD = +5 В представлены на следующем рисунке.

Таким образом, в «области проводимости», обозначенной на рисунке как «неопределённое состояние», КМОП–инвертор ведёт себя как инвертирующий усилитель с весьма высоким коэффициентом передачи.

Для входных сигналов логических уровней он фактически представляет собой два ключа, управляемых входным напряжением.

При входном сигнале VA высокого логического уровня замыкается ключ S(0), подающий на выход Y низкий потенциал GND (логический уровень «0»), при этом ключ S(1) разомкнут. А при входном сигнале VA низкого логического уровня замыкается ключ S(1), подающий на выход Y высокий потенциал +VDD (логический уровень «1»), в то время как ключ S(0) разомкнут.

Очевидно, что схемотехника КМОП–инвертора весьма проста даже при наличии в его полной электрической схеме защитных элементов по входу и выходу.

Рассмотрев схемотехнику двоичного КМОП–инвертора, используем его схемотехнические решения по индукции для создания логического элемента, реализующего функцию троичного отрицания (троичной инверсии), далее.