Троичный КМОП–инвертор

(троичное логическое отрицание, «НЕ»)

Как было выяснено ранее, для входных сигналов логических уровней КМОП–инвертор двоичной логики фактически представляет собой два ключа, управляемых входным напряжением.

При этом схемотехника двоичного КМОП–инвертора весьма проста даже при наличии в его полной электрической схеме защитных элементов по входу и выходу.

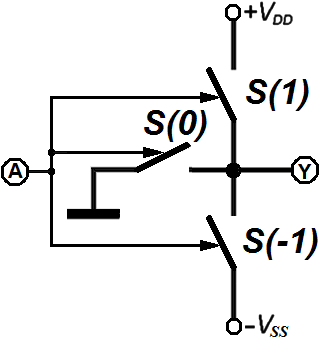

Эти факторы диктуют очевидное решение — выполнить логический элемент, реализующий функцию троичного отрицания (троичной инверсии), используя схемотехнические решения, характерные для его двоичного КМОП аналога. С этой целью кроме шины питания +VDD, отвечающей совместно с ключом S(1) за формирование высокого логического уровня (логической «1»), вводится шина питания –VSS, отвечающая совместно с вновь вводимым ключом S(–1) за формирование низкого логического уровня (логической «–1»).

Очевидно, что ключи S(1) и S(–1) также, как и в двоичном КМОП–инверторе, логично выполнить на основе полевых МОП–транзисторов с индуцированным каналом нормально закрытого типа, работающих в режиме обогащения: с каналом P-типа (верхний ключ S(1)) и каналом N-типа (нижний ключ S(–1)), хотя пороговые напряжения у этих транзисторов будут несколько иные.

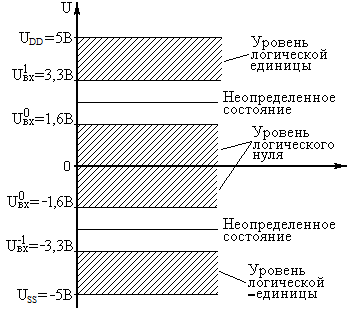

Сложнее обстоит ситуация со схемотехническим воплощением ключа S(0). Рассмотрим по индукции логические уровни сигналов для гипотетического троичного КМОП–инвертора, взяв за основу графики, характерные для его двоичного прототипа.

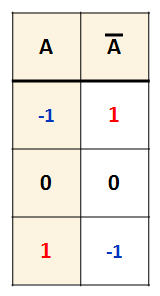

Если напомнить таблицу истинности функции троичной инверсии,

то сценарий поведения ключей S(1), S(0), S(–1) будет выглядеть следующим образом.

При подаче на вход A пилообразного напряжения VA в диапазоне от ‑5 В до +5 В, ключ S(1) будет закрываться из полностью открытого состояния, соответствующего уровню логической «1». Начиная примерно с уровня ‑2.5 В, ключ S(0) начнёт приоткрываться, поскольку инверсия троичного логического «0» есть непосредственно сам «0». Ближе к потенциалу ‑1.6 В, ключ S(0) откроется полностью, а ключ S(1) будет полностью закрыт. Открытое состояние ключа S(0) будет поддерживаться в диапазоне входного напряжения VA от ‑1.6 В до +1.6 В, после чего этот ключ будет закрываться из полностью открытого состояния, соответствующего уровню троичного логической «0», а ключ S(‑1) начнёт приоткрываться, готовясь осуществить инверсию логической «1». Примерно на уровне +3.3 В, ключ S(0) полностью закроется, а ключ S(‑1) будет полностью открыт, осуществляя подачу на выход Y низкого потенциала ‑VSS — уровня логической «‑1»).

Отметим, что ключ S(0) в диапазоне входного напряжения VA от ‑1.6 В до +1.6 В, в том числе и при VA = 0 В, полностью открыт, а вне этого диапазона закрывается. Такое поведение ключа может обеспечить комплементарная пара нормально открытых МОП–транзисторов со встроенными каналами (Depletion Mode) P-типа и N-типа, включенных последовательно. В таком случае схемотехника логического элемента, реализующего функцию троичного отрицания (троичной инверсии) приобретёт следующий вид:

Подобное схемотехническое решение включает в свой состав минимальное количество МОП–транзисторов и известно довольно давно. Схемотехника троичных логических элементов на такой элементной базе была весьма подробно рассмотрена авторами работы [Depletion/Enhancement CMOS For a Low Power Family of Three-Valued Logic Circuits] ещё в 1985 году. К сожалению, возможности технологии того времени позволили авторам разработать логические элементы, работающие в диапазоне питающих напряжений лишь от ‑1 В до +1 В, что довольно мало даже в рамках существующей в наши дни тенденции к снижению напряжения питания логических элементов КМОП технологии.

Технология производства КМОП элементов развивалась, и в 2000 году к идее создания троичных логических элементов на базе нормально закрытых и нормально открытых КМОП–транзисторов вновь обратился автор работы [Исследование трехуровневых логических устройств]. Следует отметить, что производство в едином технологическом цикле КМОП–транзисторов нормально закрытых и нормально открытых с каналами P- и N-типов, действительно, приводит к увеличению количества технологических операций, и создание транзисторов с высоким уровнем порогового напряжения также имеет некоторые сложности, но, тем не менее, это не является непреодолимым технологическим препятствием по состоянию на сегодняшний день.

Ещё в 2000 году автор отмечал: “Использование элионной технологии позволяет на одном кристалле создавать МДП–структуры с индуцированными и встроенными каналами, со сколь угодно малыми пороговыми напряжениями с устойчивым процентом выхода годных кристаллов в процессе производства. Малые пороговые напряжения транзисторов позволяют снизить напряжение питания схем. Независимая подгонка пороговых напряжений разных транзисторов одного кристалла может осуществляться путем ионной имплантации сквозь подзатворный окисел ионов примесей.”

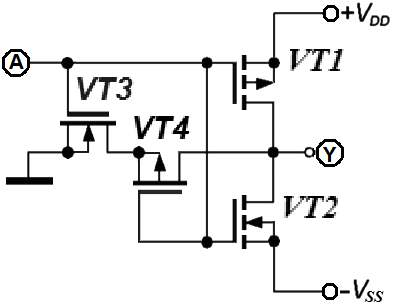

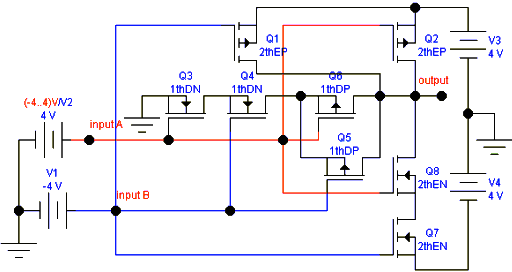

Ниже представлена схема разработанного автором варианта троичного инвертора.

Если придерживаться принятых на данной схеме обозначений, то в ней задействованы КМОП–транзисторы следующих типов: 1thDN, 1thDP, 2thEN, 2thEP, что в принятой автором терминологии означает КМОП–транзисторы со встроенным каналом (Depletion Mode N–Channel, Depletion Mode P–Channel) и низким пороговым напряжением (1th Gate-Threshold Voltage), а также с индуцированным каналом (Enhancement Mode N–Channel, Enhancement Mode P–Channel) и высоким пороговым напряжением (2th Gate-Threshold Voltage).

Если уровни напряжения источников питания положительной и отрицательной полярностей равны друг другу по абсолютной величине, т.е. питание симметрично: |+Udd| = |–Uee| = Uпит., то высокое пороговое напряжение U02 = 1,5 Uпит, соответствует КМОП–транзисторам, маркированным как 2th, а низкое пороговое напряжение U01 = 0,5Uпит — КМОП–транзисторам, обозначенным, соответственно, 1th.

По состоянию на 2000 год в номенклатуре отечественных МОП–транзисторов не был известен только прибор со встроенным каналом P–типа (Depletion Mode P–Channel). Приборы такого типа, действительно, несколько задержались в разработке, и это создало устойчивое мнение, что их не существует в принципе. В дальнейшем это вынудило производителей выпустить специальную литературу, разъясняющую разработчикам электронных схем принципы применения КМОП–транзисторов со встроенным каналом [An introduction to Depletion-mode MOSFETs].

Подведя итог изложенному выше, следует признать, что по состоянию на сегодняшний день явных технологических препятствий для реализации представленных схемотехнических решений в интегральном исполнении не имеется. Консультации с технологами отечественных предприятий, где существует соответствующее производственное оборудование, подтвердили, что устройства такого типа вполне можно производить по технологическим нормам, соответствующим хотя бы серии К561, при соответствующем финансировании и проведении необходимой опытно-конструкторской разработки.

В этой связи целью проведенного исследования было создание моделей необходимых устройств троичной логики, позволяющих разработать троичную процессорную систему на их основе.

В процессе разработки выяснилось, что предложенные автором работы [Исследование трехуровневых логических устройств] модели имеют невысокую нагрузочную способность (что, в общем-то, характерно для микросхем КМОП), и при создании на их основе более сложных устройств, а также при работе на емкостную нагрузку наблюдается искажение формируемого ими сигнала.

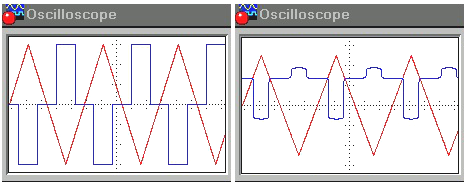

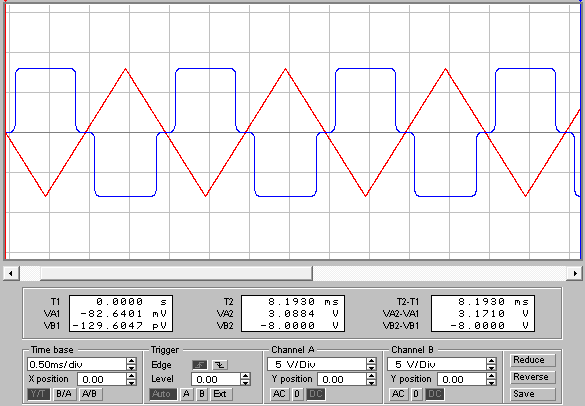

Ниже представлены осциллограммы входного и выходного сигналов модели троичного инвертора на холостом ходу (слева) и при подключении на выход нескольких идентичных инверторов с емкостной нагрузкой порядка 10..50 пФ (справа).

Проведенный анализ показал, что при создании троичных логических схем автором были использованы так называемые "идеальные" (ideal) модели полевых транзисторов с изолированным затвором, соответствующие приборам малой мощности с некими усредненными характеристиками.

Как показала практика, "идеальные" модели МОП–транзисторов не способны обеспечивать в нагрузку ток порядка 1 мА, чтобы обеспечивать нагрузочную способность хотя бы 1 входа элементов ТТЛШ для совместимости с ними в сложных цифровых схемах.

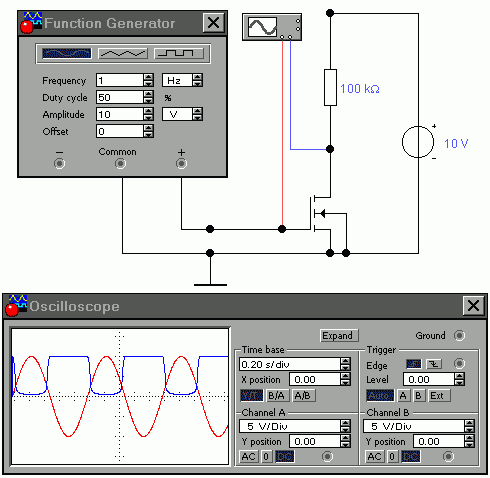

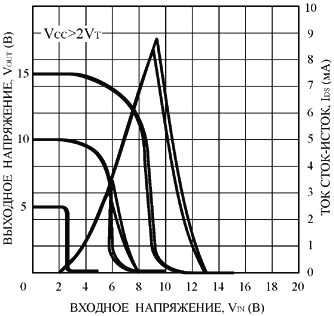

Ниже представлены иллюстрации работы каскада с общим истоком на основе "идеальной" модели МОП–транзистора при нагрузке в 100 кОм и 10 кОм, питающем напряжении 10 В и входном синусоидальном сигнале.

Очевидно, что "идеальная" модель МОП–транзистора не способна обеспечивать в нагрузку ток порядка 1 мА, поэтому с целью достижения требуемых нагрузочных характеристик, необходимо заменить "идеальные" модели на подходящие модели реально существующих полевых транзисторов с изолированным затвором. При этом основным критерием подбора замены были следующие требования: транзисторы малой мощности должны были иметь соответствующие модели в библиотеке системы разработки, но и существовать в физическом доступе в настоящее время, поскольку сам пакет схемотехнического моделирования является всё же несколько устаревшим на сегодняшний день.

Обзор открытых источников показал, что довольно часто двоичный инвертор в выбранном пакете схемотехнического моделирования реализуют на основе пары маломощных МОП–транзисторов 2N7002–BSS84.

2N7002 — Маломощный N–канальный полевой транзистор с изолированным затвором, логическим уровнем управления и низким сопротивлением в открытом состоянии.

- ёмкость: 20…25 пФ;

- пороговое напряжение включения: 2.. 3 В;

- время включения/выключения: 2.5/11 нс;

- максимальный ток стока: 0.2 А;

- сопротивление сток-исток открытого транзистора: 5 Ом.

BSS84 — Маломощный P–канальный полевой транзистор c изолированным затвором (вертикальный D-MOS) в корпусе SOT-23.

- ёмкость: 25 пФ;

- напряжение открывания на затворе: -0,8..-2,0 В;

- время включения/выключения: 3/7 нс;

- максимальный ток стока:13 А;

- сопротивление сток-исток открытого транзистора: < 10 Ом.

Транзисторы являются довольно распространенными, судя по каталогам поставщиков, и, согласно приведённым выше параметрам, вполне могут работать как комплементарная пара, что подтвердилось при моделировании на их основе схемы двоичного инвертора.

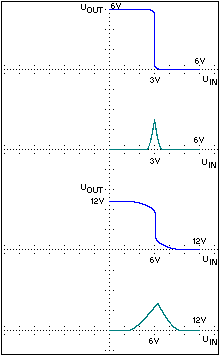

Измеренные передаточные характеристики модели двоичного КМОП–инвертора при разных значениях питающего напряжения (слева) хорошо коррелируют с графиками (справа), приведенными в литературе для реального КМОП–инвертора.

|

|

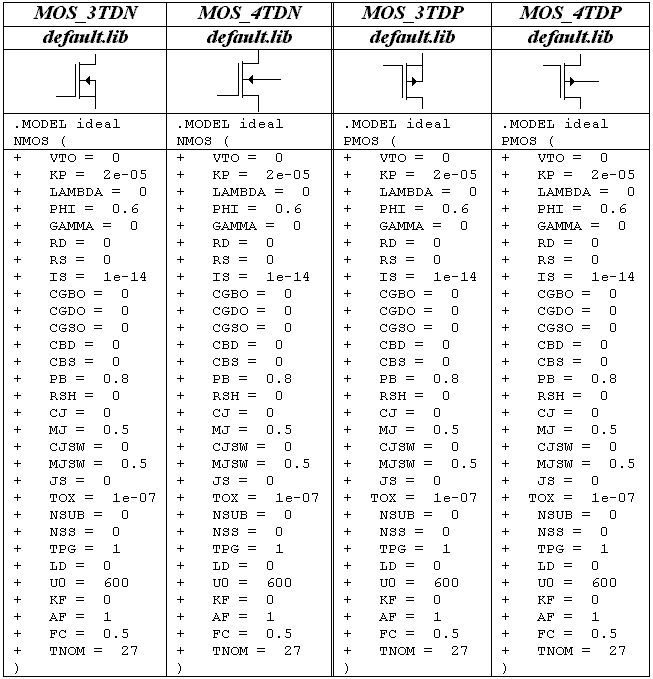

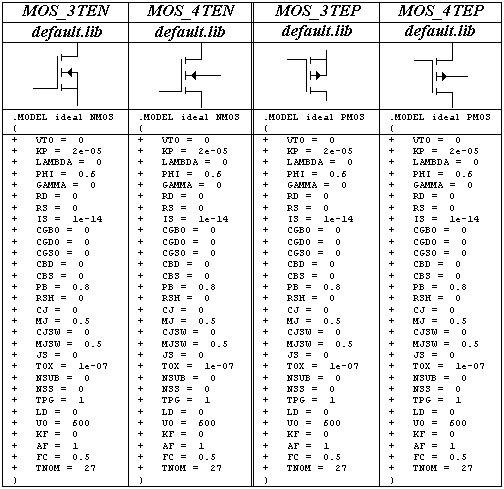

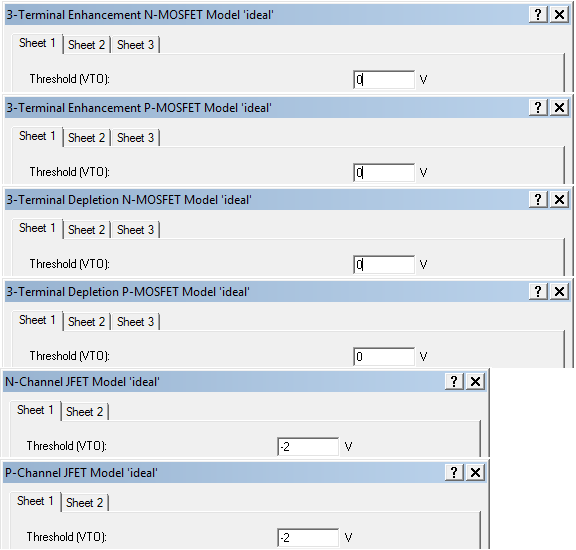

В процессе редактирования библиотек КМОП–транзисторов используемого пакета схемотехнического моделирования выяснилось, что все модели "идеальных" МОП–транзисторов практически идентичны по большинству параметров за исключением самых характерных, определяющих тип и проводимость.

Ниже приведены модели "идеальных" трёх- и четырёхвыводных МОП–транзисторов нормально закрытых (Enhancement Mode MOSFET) с каналами N– и P–типов.

Таблицу

Модели "идеальных" трёх- и четырёхвыводных МОП–транзисторов нормально открытых (Enhancement Mode MOSFET) с каналами N– и P–типов представлены на следующей вкладке.

Таблицу

Очевидно, что автор работы [Исследование трехуровневых логических устройств] изменял в них лишь параметр порогового напряжения при создании своих моделей троичных логических элементов, что довольно логично, поскольку пара полевых транзисторов является комплементарной, если они обладают каналами противоположного типа проводимости, а по остальным параметрам идентичны.

По аналогии с моделями "идеальных" трёх- и четырёхвыводных МОП–транзисторов были созданы модели МОП–транзисторов с реальной нагрузочной способностью на основе параметров маломощного полевого транзистора с изолированным затвором 2N7002.

В процессе создания библиотек также была изменена привязка пороговых напряжений вновь создаваемых моделей КМОП–транзисторов.

Если автор работы [Исследование трехуровневых логических устройств] выбрал пороги включения моделей КМОП–транзисторов, исходя из величин выбранных им напряжений питания ±4 В, что в совокупности составляет 8 В питающего напряжения.

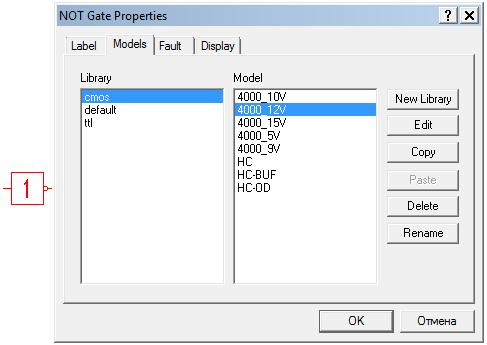

Для вновь создаваемых моделей КМОП–транзисторов напряжение питания было выбрано равным 12 В (±6 В) с целью обеспечения совместимости с имеющимся в пакете схемотехнического моделирования 12–вольтовым семейством логических элементов CD4000 (отечественный аналог – серия К561, являющаяся более распространённой, нежели ранняя серия К176 – аналог CD4000A).

Известно, что КМОП–серии логических элементов способны работать в широком диапазоне питающих напряжений — от 3 В до 15 В, но в рамках данного пакета имеющиеся в нём модели логических КМОП–элементов являются цифровыми, то есть, не имеют свойств аналогового инвертирующего усилителя, формируют лишь характерные задержки распространения и реагируют на строго определённые логические уровни. Именно поэтому в библиотеке эти элементы разделены на группы по критерию величины питающего напряжения.

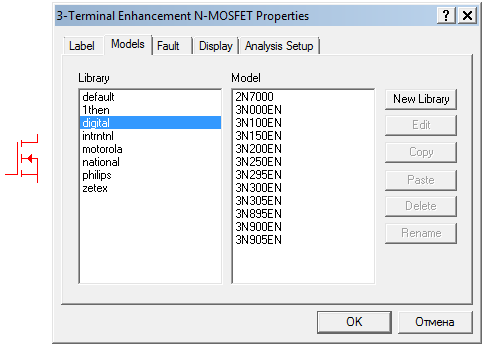

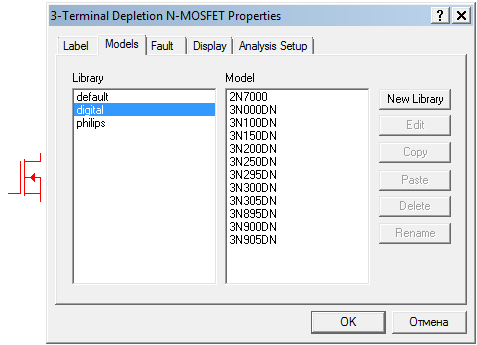

В итоге для моделирования троичных логических элементов была создана библиотека “digital” (“цифровые”), содержащая следующие типы N–канальных МОП–транзисторов.

МОП–транзисторы N–канальные с индуцированным каналом обогащённого типа — нормально закрытые (N–Channel Enhancement Mode MOSFET).

МОП–транзисторы N–канальные со встроенным каналом обеднённого типа — нормально открытые (N–Channel Depletion Mode MOSFET).

Модель маломощного МОП–транзистора 2N7002 внесена в библиотеку в качестве образца реально существующего транзистора.

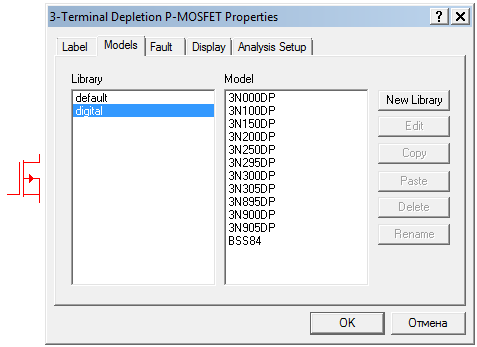

Библиотека также включала следующие типы P–канальных МОП–транзисторов.

МОП–транзисторы P–канальные с индуцированным каналом обогащённого типа — нормально закрытые (P–Channel Enhancement Mode MOSFET).

МОП–транзисторы P–канальные со встроенным каналом обеднённого типа — нормально открытые (P–Channel Depletion Mode MOSFET).

Модель маломощного МОП–транзистора BSS84 также была внесена в библиотеку, как образец реально существующего транзистора.

Для удобства в работе, и для того, чтобы транзисторы для моделирования троичных логических элементов отличались от прочих, имеющихся в данном программном пакете моделей реальных транзисторов, было принято специфическое обозначение типа:

3NVvvXY, где 3N условно обозначает серию транзисторов для моделирования троичных логических элементов;

Vvv — пороговое напряжение с точностью до второго знака (V – вольты, vv – десятые и сотые доли вольт);

X — тип транзистора (E – Enhancement Mode, D – Depletion Mode);

Y — тип проводимости канала (N–Channel, P–Channel).

К примеру: 3N295EN — МОП–транзистор для моделирования троичных логических элементов с пороговым напряжением 2,95 Вольт, с индуцированным каналом обогащённого N–типа (N–Channel Enhancement Mode MOSFET).

Необходимо подчеркнуть, что термин «пороговое напряжение» справедлив лишь для нормально закрытых МОП–транзисторов с индуцированным каналом, и по определению это напряжение между затвором и истоком при котором ток канала достигает определённой малой величины, обычно 10 мкА. В зарубежной литературе и справочных материалах этот параметр принято обозначать как VGS TH — “Gate to Source Threshold Voltage” — “напряжение порога затвор–исток”.

Поскольку нормально открытые МОП–транзисторы со встроенным каналом проводят ток и при нулевом напряжении затвор–исток, для них существует другой термин, обозначающий порог, при котором ток канала уменьшается до определённой малой величины, обычно те же 10 мкА. Но этот параметр принято называть «напряжение отсечки». Тем не менее, в справочных материалах для обоих типов транзисторов этот параметр довольно часто обозначают как VGS TH, хотя встречается и правильное обозначение — VGS(off) — “Gate Source Cutoff Voltage”.

В обсуждаемом пакете схемотехнического моделирования для всех типов полевых транзисторов этот параметр обозначается совершенно одинаково: “Threshold (VT0)”, поэтому в тексте здесь он упоминается также просто — «пороговое напряжение».

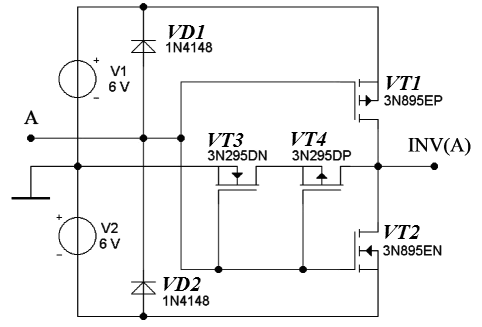

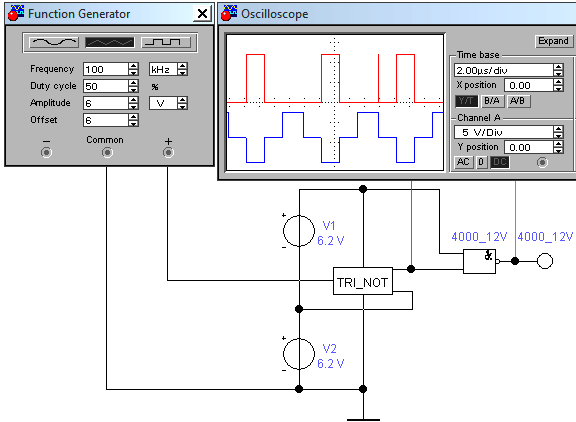

Ниже приведена принципиальная электрическая схема троичного логического инвертора, разработанного на основе моделей МОП–транзисторов, представленных ранее.

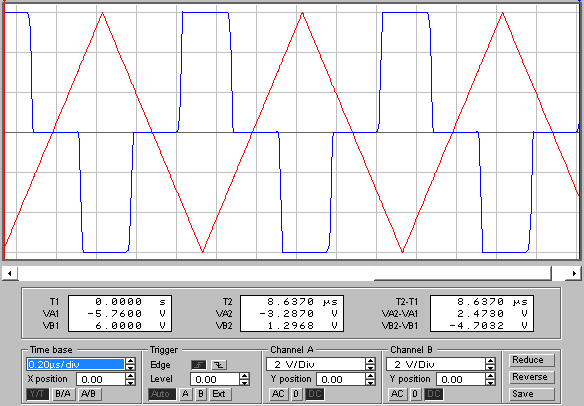

На рисунках ниже приведены осциллограммы входного пилообразного сигнала (красный цвет) и выходного сигнала троичного инвертора (синий цвет) при работе на нагрузку 10 кОм, 50 пФ, на частоте входного пилообразного сигнала — 100 кГц.

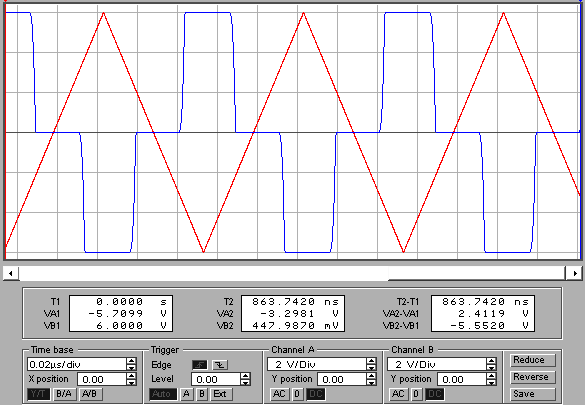

На частоте входного сигнала 1 МГц.

На частоте входного сигнала 10 МГц.

Для сравнения ниже приведены осциллограммы входного пилообразного сигнала и выходного сигнала троичного инвертора при работе на частоте входного сигнала 10 МГц без нагрузки (на холостом ходу).

Исследование модели троичного логического инвертора, разработанного на основе предложенных Spice–моделей МОП–транзисторов, показало, что он уверенно отдаёт в нагрузку ток порядка 1 mA и способен работать на емкостную нагрузку порядка 50 пФ без существенных искажений выходного сигнала.

На рисунке ниже представлена переходная характеристика модели троичного логического инвертора, измеренная на частоте 1 кГц.

Необходимо указать, что известны и более точные модели МОП–транзисторов, соответствующие непосредственно этим полупроводниковым приборам в интегральном исполнении [SPICE Model for NMOS and PMOS FETs in the CD4007].

Но предложенные автором указанной выше работы SPICE–модели являются моделями седьмого уровня (Level 7) программы PSpice, с которыми данный пакет схемотехнического моделирования работать не способен.

Как показало исследование, предложенные в нашей работе модели позволяют вполне адекватно симулировать поведение троичного логического инвертора как аналогового устройства.

Троичный логический инвертор был оформлен в виде компактного модуля, предназначенного для применения в составе более сложных цифровых троичных устройств. Рисунок ниже иллюстрирует совместимость троичного инвертора с логическим вентилем «И-НЕ» 12–вольтового семейства логических элементов CD4000.

На приведённых на рисунке осциллограммах видно, что троичный логический инвертор совместим по логическим уровням «+1» и «–1» с КМОП–логическим вентилем «И-НЕ» 12–вольтового семейства логических элементов CD4000, но троичный логический уровень «0» может вызвать сбой в работе двоичного вентиля и формирование помехи типа «иголка».

Возможность произвольно устанавливать пороги переключений в моделях позволила исследовать влияние разности порогов, определяющей диапазон входного сигнала, при котором пары ключей инвертора, образованных МОП–транзисторами открыты одновременно, пропуская сквозной ток.

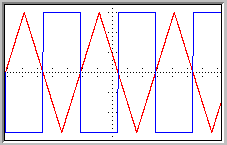

На рисунке ниже представлена осциллограмма сигналов в ситуации, когда разница между порогами открытия и закрытия МОП–транзисторов составляет примерно 1 В.

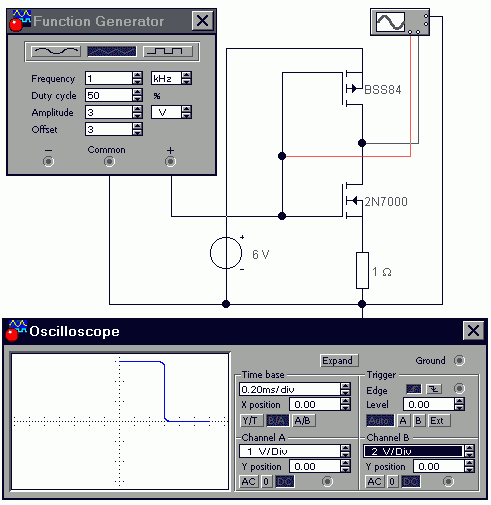

Очевидно, что наблюдаются искажения выходного сигнала, выраженные в сглаживании фронтов и срезов. Но подобный эффект не является особенностью характерной лишь для схемы троичного инвертора. На рисунках ниже представлены осциллограммы сигнала на выходе двоичного инвертора: разность порогов, определяющая диапазон входного сигнала, при котором пары ключей инвертора, образованных МОП–транзисторами открыты одновременно, составляет 0.1 В на осциллограмме слева и 3 В — на осциллограмме справа.

|

|

Исследование показало, что величина разности порогов в 0.1 В — наиболее оптимальна с точки зрения формирования неискаженного сигнала на выходе троичного инвертора, что, собственно, и определило пороговые напряжения МОП–транзисторов в его схеме: –2.95 В, –8.95 В, +2.95 В, +8.95 В.

Поскольку обсуждаемая схема троичного инвертора известна давно, но с тех пор из открытых источников неизвестно, проводилось ли наряду с численным моделированием её макетирование. Это отмечается в работе [Исследование возможностей и способов реализации современных троичных цифровых элементов], где также высказывается сомнение в эффективной работоспособности составного ключа из двух нормально открытых КМОП–транзисторов, коммутирующего на выход потенциал логического «0».

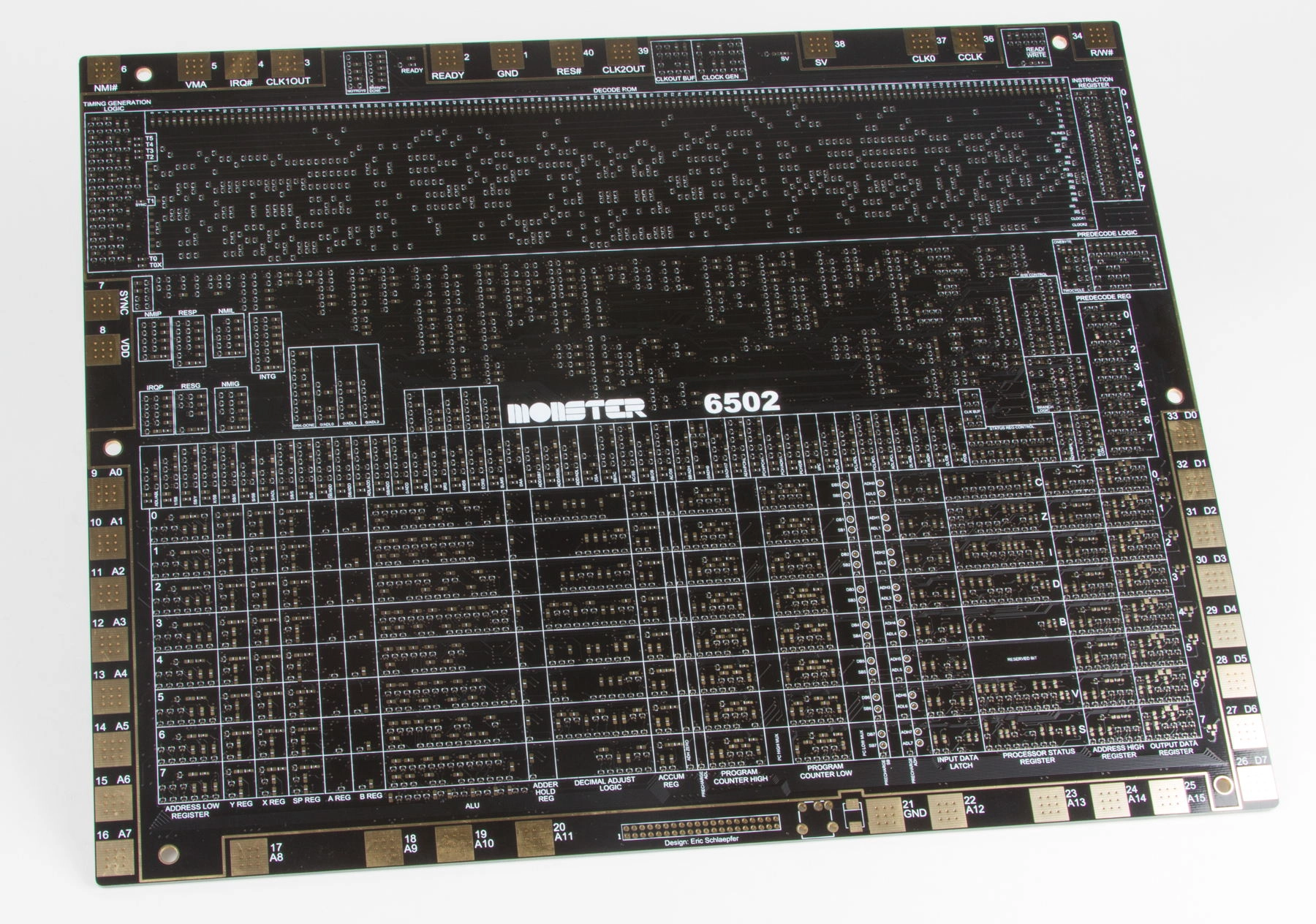

Привлекательной представлялась также возможность выполнить макет троичного процессора на дискретных SMD компонентах по технологии поверхностного монтажа, как это сделал автор проекта [The MOnSter 6502], создавший действующий аналог легендарного 8-разрядного микропроцессора MOS 6502 из отдельных дискретных компонентов на плате размером 380 x 305 мм.

[The MOnSter 6502]

Для проверки работоспособности троичного инвертора, разработанного согласно обсуждаемым выше схемотехническим решениям, было проведено его макетирование на дискретных компонентах.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download