Логические элементы троичной конъюнкции ("MIN","И")

Чтобы процесс построения троичного логического элемента, реализующего функцию конъюнкции, был более понятен, приведём классическое определение конъюнкции.

Конъюнкция — логическая операция, действие которой по смыслу максимально приближенно к реализуемому союзом «и». Синонимы: логическое «И», логическое умножение, иногда просто «И». Конъюнкция может быть бинарной операцией, тернарной (троичной) операцией, или n–арной операцией.

Иначе говоря, результатом этой операции является пересечение двух или более множеств в графическом представлении.

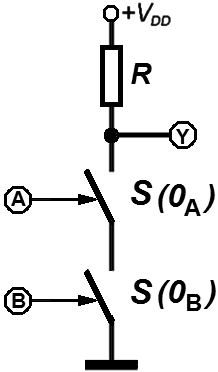

С точки зрения электрических цепей реализация данной логической операции также достаточно проста.

Через резистор R будет проходить ток, а, следовательно, на выходе Y появится потенциал низкого уровня, если, согласно воздействиям на входах A и B будут одновременно замкнуты ключи S(0A) «И» S(0B). Если хотя бы один из этих ключей не замкнут, ток через резистор R не проходит, и на выходе Y удерживается потенциал высокого уровня. Собственно, если воспринимать замыкание ключей сигналами на входах A и B как события истинные (лог. «1»), то представленная выше электрическая цепь реализует логическую операцию инверсии конъюнкции двух входных аргументов, иначе говоря, функцию «И–НЕ» (NAND – Not AND).

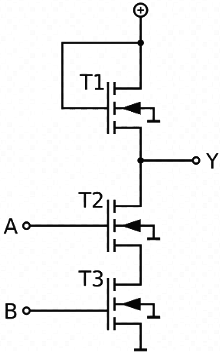

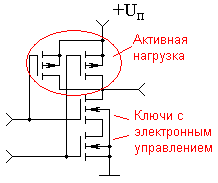

По такому принципу, собственно, и строились логические элементы на заре МОП–технологии. Ниже представлена схема логического элемента, выполненного по технологии N–МОП (NMOS).

В N–МОП (или P–МОП) технологии в качестве резистора нагрузки R применяется стабилизатор тока на транзисторе T1. Этот транзистор имеет индуцированный канал, и представляет собой фактически аналог резистора с большим динамическим сопротивлением. N–МОП транзисторы T2 и T3, включенные последовательно, играют роль ключей S(0A) и S(0B), соответственно.

Прежде чем высказать критические замечания в адрес представленной выше схемы логического N–МОП вентиля, напомним, что по технологии N–МОП был выполнен легендарный ныне микропроцессор К580ВМ80А (отечественный функциональный аналог i8080).

Микропроцессор мог работать на частоте до 4 МГц, но потреблял при этом до 1,5 Вт электрической мощности, то есть, при работе микропроцессор был реально горячим!

Не умаляя исторических заслуг упомянутого микропроцессора, этот факт подчеркивает основной недостаток логических элементов, выполненных по N–МОП (или P–МОП) технологии: в состоянии лог. «0» на выходе они бесполезно потребляют энергию от источника питания и рассеивают её на кристалле. Этого недостатка лишены логические элементы, выполненные по технологии КМОП.

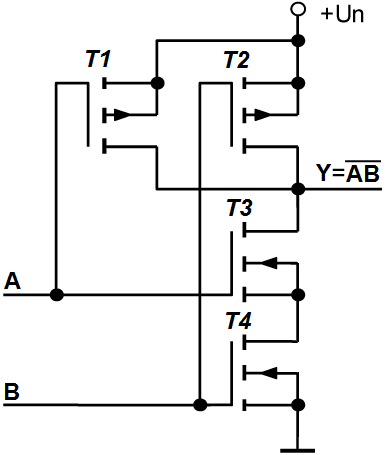

Перейдём к принципам построения логического элемента «И–НЕ» по технологии КМОП, с учетом всех нюансов, рассмотренных при обсуждении принципов действия КМОП–инвертора.

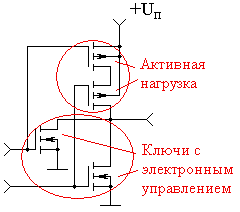

Как видно из рисунка выше, ключи S(0A) и S(0B), соединённые последовательно и коммутирующие низкий потенциал лог. «0» на выход Y, собственно, и реализуют логику операции «И». Ключи же S(1A) и S(1B) соединены параллельно, работают в противофазе ключам S(0A) и S(0B), и образуют для них так называемую динамическую нагрузку.

Если, согласно воздействиям на входах A и B, ключи S(0A) и S(0B) будут одновременно замкнуты, то ключи S(1A) и S(1B) будут одновременно разомкнуты, и на выход Y, поступит низкий потенциал лог. «0». Если же хотя бы один из ключей S(0A) и S(0B) не замкнут, то обязательно замкнут соответствующий ему ключ S(1A) или S(1B). Через один из них, следовательно, на выход Y подаётся потенциал высокого уровня, соответствующий лог. «1». Так реализуется логика работы элемента «И–НЕ» по технологии КМОП. Схема элемента на КМОП–транзисторах, представленная ниже, полностью реализует схемотехнически это качественное описание с помощью ключей.

Имея перед собой схему двоичного КМОП–вентиля «И–НЕ», преобразуем её для выполнения логических операций с троичными уровнями. КМОП–транзисторы T1 и T2 в схеме троичного КМОП–вентиля «И–НЕ» будут выполнять аналогичную функцию — коммутировать на выход Y высокий потенциал, соответствующий лог. «1». КМОП–транзисторы T3 и T4 также будут выполнять в схеме характерную для них функцию — коммутировать на выход Y низкий потенциал, но в троичной логике он соответствует лог. «–1». Пороги включения этих транзисторов будут увеличены, также как это было сделано в схеме троичного инвертора.

Осталось уяснить, как будут подключены в схему дополнительные транзисторы, коммутирующие на выход Y потенциал, соответствующий лог. «0» троичной логики, в которой он соответствует понятию «НЕИЗВЕСТНО», «НЕОПРЕДЕЛЕНО».

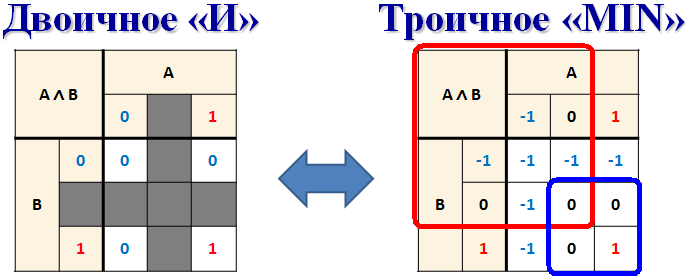

Рассмотрим с этой целью в сравнении таблицы истинности вентилей «И» двоичной и троичной логики, которые уже приводились ранее.

Проследим за предполагаемой логикой работы троичного вентиля «И–НЕ», учитывая инверсию выходного сигнала.

Если включены оба КМОП–транзистора T1 и T2, то непременно должны быть выключены транзисторы T3 и T4, и на выход Y поступает высокий потенциал, соответствующий лог. «1». В этом случае дополнительные транзисторы, коммутирующие на выход Y потенциал, соответствующий лог. «0» троичной логики также должны быть выключены.

Если включены оба КМОП–транзистора T3 и T4, то транзисторы T1 и T2 должны быть выключены, следовательно, на выход Y поступает низкий потенциал, соответствующий лог. «–1». И в этом случае дополнительные транзисторы, коммутирующие на выход Y потенциал, соответствующий лог. «0» троичной логики также должны быть выключены. Такой вывод следует из совместимости троичной логики с двоичной по логическим уровням, соответствующим понятиям «ИСТИННО» и «ЛОЖНО».

Теперь рассмотрим две таблицы, выделенные на рисунке Троичное «MIN» красным и синим контурами. Внимательно проанализировав их, можно увидеть, что и та, и другая соответствую таблице истинности для двоичного элемента «И», но в таблице, выделенной синим контуром в роли понятия «ЛОЖНО» выступает лог. «0» троичной логики, а в таблице, выделенной красным контуром, он выступает как раз в роли понятия «ИСТИННО». Что, собственно, не противоречит введённому ранее понятию троичного лог. «0», но явно подсказывает, какой должна быть топология ключа, коммутирующего на выход Y потенциал, соответствующий лог. «0» троичной логики в троичном вентиле «И–НЕ»: она должна быть полностью аналогичной топологии двоичного элемента «И–НЕ».

Рассмотрим на рисунке ниже, как это выглядит с точки зрения схемотехники.

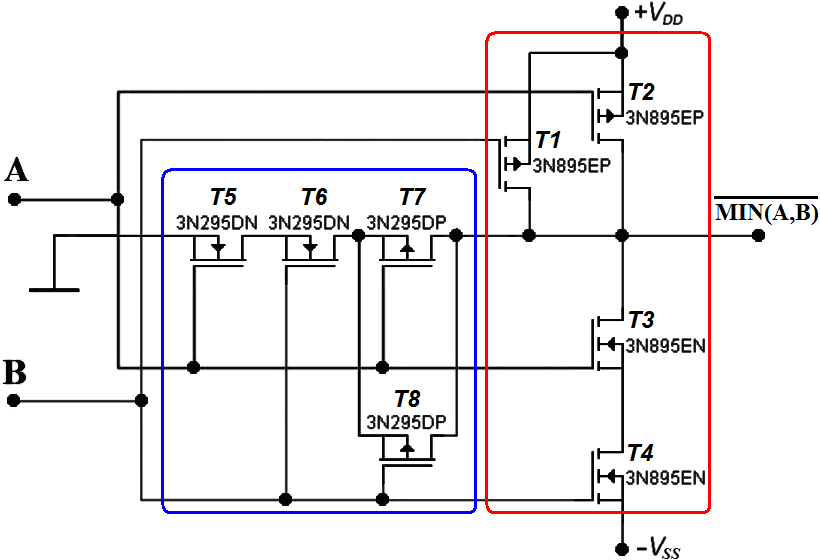

На схеме выше красным контуром выделена часть схемы, которая фактически выполняет операцию двоичного «И–НЕ» с троичными логическими уровнями, соответствующими понятиям «ИСТИННО» и «ЛОЖНО». Синим контуром выделена идентичная ей по топологии часть схемы, выполняющая фактически операцию двоичного «И–НЕ» с троичными логическими уровнями, соответствующими понятиям «ИСТИННО»–«НЕИЗВЕСТНО», а также с «НЕИЗВЕСТНО»–«ЛОЖНО».

То есть, в то время, когда идёт работа троичного логического элемента «INV–MIN» с логическими уровнями «ИСТИННО» и «ЛОЖНО», работает часть схемы, выделенная красным контуром. Часть схемы, выделенная синим контуром, в это время заблокирована входными сигналами. Если же на входе троичного логического элемента «INV–MIN» появляется сигнал «НЕИЗВЕСТНО», то часть схемы, выделенная синим контуром, выполняет функцию двоичного «И–НЕ» либо с транзисторами T1 и T2, из красного контура, либо же с транзисторы T3 и T4.

Так, собственно, схема троичного логического элемента «INV–MIN» реализует логическую операцию инверсии конъюнкции: на выход троичного логического вентиля «INV–MIN» проходит с инверсией минимальный из двух входных сигналов. По уровню, соответствующему троичной лог. «1» на одном из входов, вентиль «INV–MIN» прозрачен для любых троичных входных сигналов на другом входе. По уровню, соответствующему троичному лог. «0», вентиль «INV–MIN» прозрачен для троичного сигнала лог. «–1». По уровню, соответствующему троичному лог. «–1» на одном из входов, вентиль «INV–MIN» непрозрачен для любых сигналов.

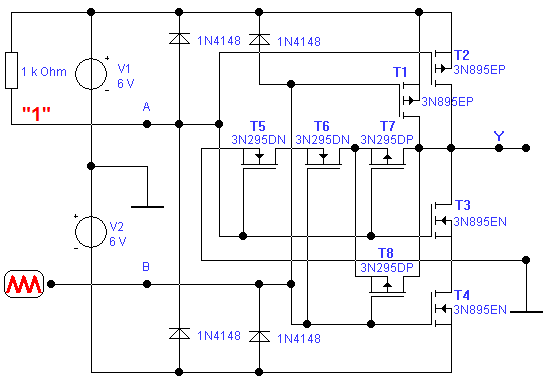

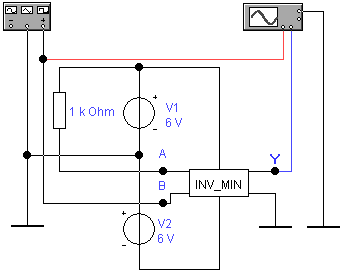

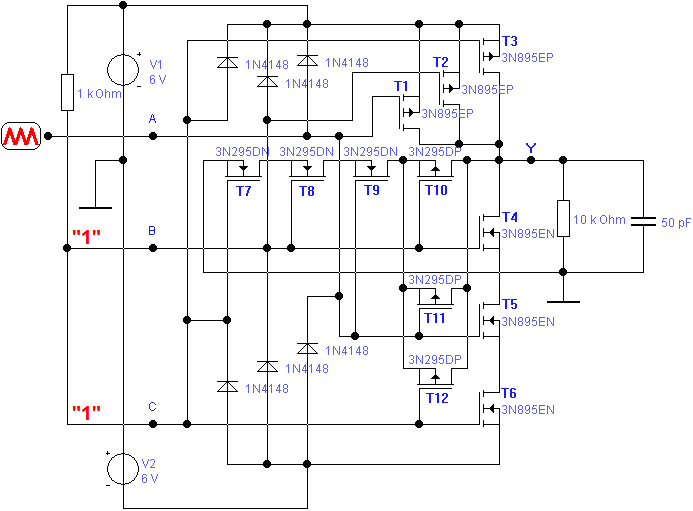

Ниже представлена модель троичного логического элемента «INV–MIN», выполненная в программе схемотехнического моделирования.

На входах схемы подключены защитные диоды, которые при моделировании привносят свой вклад во входную ёмкость модели троичного логического элемента «INV–MIN».

Схема включает в себя два источника напряжения V1 и V2, которые обеспечивают симметричное питание ±6 В, а также КМОП–транзисторы, образующие, как это рассматривалось ранее, "ключи", коммутирующие на выход схемы Y либо положительную шину питания (+6 В), либо потенциал общего провода ("земли"), либо отрицательную шину питания (–6 В), в зависимости от комбинации входных сигналов А и B. Рассмотрим подробнее логику работы данных "ключей".

"Ключ", подключающий выход схемы к положительной шине питания, состоит из двух параллельно включенных МОП–транзисторов T1 и T2 с индуцированным p–каналом и пороговым напряжением –8.95 В (3N895EP). Поскольку их подложки подключены к истокам, которые в свою очередь подсоединены к положительному полюсу источника питания (+6 В), то каждый из них открывается при напряжении на затворе меньшем, чем –2.95 В. Затворы транзисторов T1 и T2 подключены к входам А и B . Таким образом, выход схемы оказывается подключенным к положительной шине питания либо когда напряжение на входе А меньше –2.95 В, либо когда напряжение на входе B меньше –2.95 В. Иными словами, состояние лог. «1» на выходе возникнет в том случае, если на один из входов придёт лог. «–1».

Рассмотрим "ключ", связывающий выход схемы с общим проводом. Он состоит из параллельно соединённых МОП–транзисторов T7 и T8 с встроенным каналом p–типа и напряжением отсечки +2.95 В (3N295DP), с которыми последовательно соединены МОП–транзисторы T5 и T6 с встроенным каналом n–типа и напряжением отсечки –2.95 В (3N295DN). Вход A подключен к затвору одного из n–канальных транзисторов T5 и к затвору одного из p–канальных транзисторов T7. К затворам оставшихся двух транзисторов T6 и T8 подключён вход B. Таким образом, чтобы выход схемы оказался подключён к потенциалу лог. «0», необходимо, чтобы был открыт хотя бы один из параллельно включенных T7 и T8, то есть при напряжении меньшем +2.95 В на входе А или входе B, а также, чтобы были открыты одновременно оба T5 и T6, то есть при напряжении на входах А и B большем –2.95 В. Иными словами, состояние лог. «0» возникнет на выходе схемы Y только в том случае, если ни на входе A, ни на входе B нет лог. «–1» (иначе отключен один из 3N295DN), а также, если на входы A и B одновременно не придут сигналы «+1» (в противном случае отключатся оба транзистора T7 и T8).

Наконец "ключ", соединяющий выход схемы с отрицательной шиной питания, состоит из двух включённых последовательно МОП–транзисторов T3 и T4 с индуцированными каналами n‑типа и пороговым напряжением +8.95 В. Поскольку их подложки подключены к истокам, которые в свою очередь соединены с отрицательной шиной источника питания (–6 В), то данные транзисторы откроются при напряжении большем +2.95 В на затворах, которые соединены с входами схемы (затвор транзистора T3 подключен к входу A, а T4 — к входу B). Таким образом, отрицательная шина питания окажется подключенной к выходу схемы только в том случае, если на обоих входах A и B напряжение превышает +2.95 В. Иными словами, состояние «–1» возникнет на выходе схемы Y только лишь в том случае, если на оба входа придут сигналы«+1».

Таблица истинности исследуемой модели троичного логического элемента «INV–MIN» приведена ниже.

Перейдём к рассмотрению результатов моделирования.

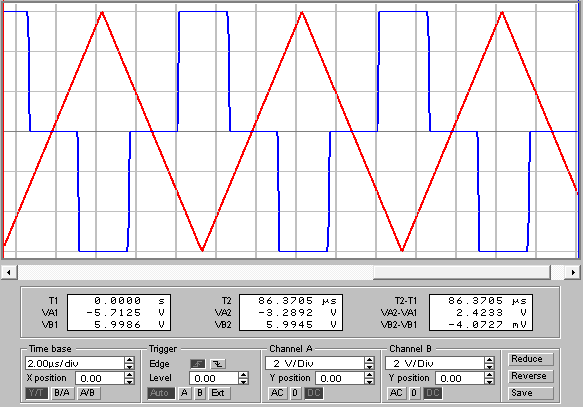

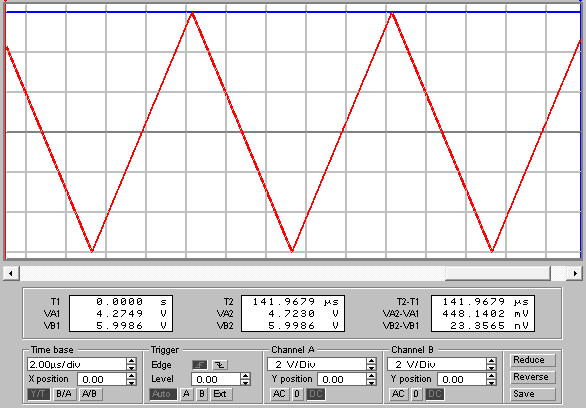

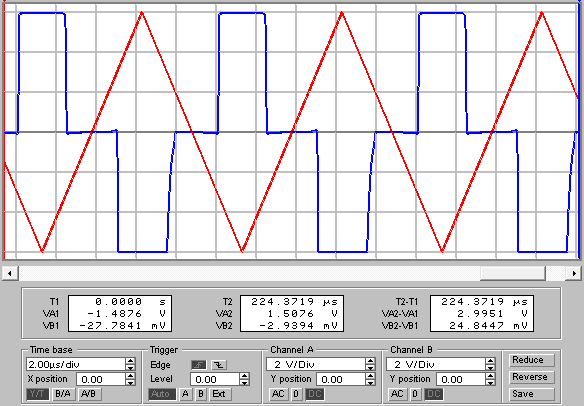

На рисунке ниже приведены осциллограммы входного пилообразного сигнала (красный цвет), поданного на вход B, и выходного сигнала троичного логического элемента «INV–MIN» (синий цвет) при работе на нагрузку 10 кОм, 50 пФ, на частоте входного пилообразного сигнала — 100 кГц. На вход A вентиля при этом через резистор номиналом 1 кОм подан сигнал лог. «1».

Очевидно, что модель троичного логического элемента «INV–MIN» демонстрирует полное соответствие своей таблице истинности. По уровню, соответствующему троичной лог. «1» на одном из входов, вентиль «INV–MIN» с точностью до инверсии прозрачен для любых троичных входных сигналов на другом входе.

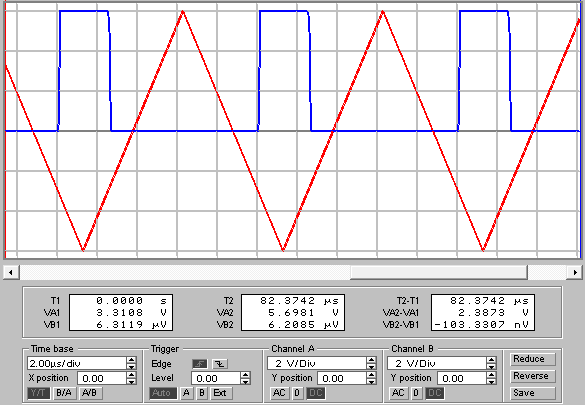

На рисунке ниже приведены осциллограммы входного пилообразного сигнала (красный цвет), поданного на вход B, и выходного сигнала троичного логического элемента «INV–MIN» (синий цвет) при работе на нагрузку 10 кОм, 50 пФ, на частоте входного пилообразного сигнала — 100 кГц. На вход A вентиля при этом непосредственно подан сигнал лог. «0».

Очевидно, что по уровню, соответствующему троичному лог. «0» на одном из входов, вентиль «INV–MIN» с точностью до инверсии прозрачен лишь для троичного сигнала лог. «–1» на другом входе.

Следующий рисунок иллюстрирует тот факт, что по уровню, соответствующему троичному лог. «–1» на одном из входов, вентиль «INV–MIN» ни для каких сигналов не прозрачен.

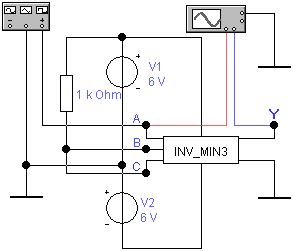

Поскольку данная модель адекватно симулирует работу троичного логического элемента «INV–MIN», она была оформлена в виде отдельного функционального модуля, который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

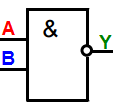

Фактически, это троичный аналог двоичного логического элемента, представленного на рисунке ниже.

На модели троичного логического элемента «INV–MIN» была также проверена возможность замены P–канального МОП–транзистора со встроенным каналом на P–канальный полевой транзистор с изоляцией затвора p-n–переходом для оценки перспективы макетирования элемента на основе дискретных компонентов. Ниже представлена соответствующая модель такого устройства.

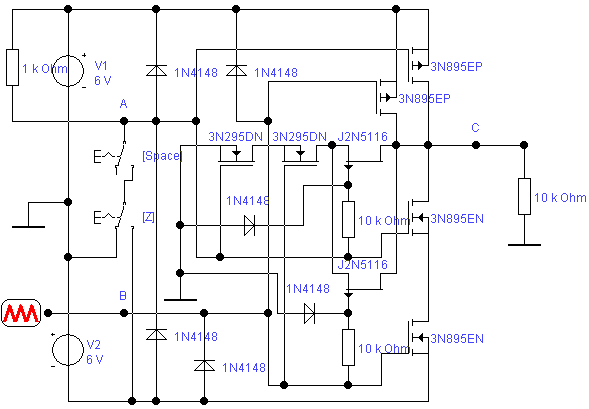

На рисунке ниже представлены осциллограммы работы модели троичного логического элемента «INV–MIN» с полевым транзистором J2N5116 в качестве замены нормально открытого P–канального МОП–транзистора со встроенным каналом при частоте входного пилообразного сигнала 100 кГц (осциллограмма красного цвета).

Также, как и при исследовании троичного инвертора, на осциллограммах видно, что форма выходного сигнала (синий цвет) незначительно искажена, в силу того, что транзистор J2N5116 с p-n–затвором затягивает фронт перехода от логической «–1» к «0», поскольку не является полностью комплементарным транзистору 3N295DN, имеет более низкое напряжение отсечки и меньшую крутизну. Но возможность замены также принципиально подтверждается, что позволяет использовать подобное схемотехническое решение при макетировании троичного логического элемента «INV–MIN».

Макетирование троичного логического элемента «INV–MIN» на дискретных элементах не проводилось, поскольку в составе многоцелевой микросхемы К176ЛП1 транзисторы с одинаковой проводимостью каналов соединены между собой как по цепям истоков, так и подложек, что не позволяет использовать их в представленной здесь схеме независимо.

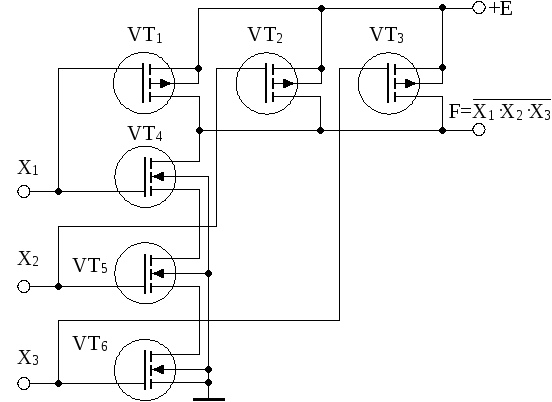

Двоичный трёхвходовый логический элемент «И–НЕ» («3И–НЕ», «3NAND»), выполненный по технологии КМОП, схема которого представлена на рисунке ниже, построен по тем же принципам, что и двухвходовый логический элемент «И–НЕ», схемотехника которого была рассмотрена ранее.

МОП–транзисторы VT1, VT2 и VT3, включенные параллельно, образуют динамическую нагрузку, для комплементарных им МОП–транзисторов VT4, VT5 и VT6, включенных последовательно с транзисторами динамической нагрузки. Затворы транзисторов VT1, VT2 и VT3 соединены попарно с затворами транзисторов VT4, VT5 и VT6, соответственно, образуя входы X1, X2 и X3 логического элемента. Транзисторы VT1 и VT4, VT2 и VT5, VT3 и VT6, работают в противофазе, при этом включенные последовательно транзисторы VT4, VT5 и VT6 фактически реализуют логику элемента «3И–НЕ». Когда на их затворах одновременно присутствует высокий уровень лог. «1», эти транзисторы открыты, и на выход F поступает низкий потенциал общего провода, соответствующий лог. «0». Транзисторы VT1, VT2 и VT3 при этом все одновременно закрыты.

Если хотя бы на одном из входов X1, X2 и X3 логического элемента присутствует низкий уровень лог. «0», то один из транзисторов VT4, VT5 или VT6 выключен, следовательно, низкий потенциал общего провода, соответствующий лог. «0», на выход F не поступает. Но в этом случае открыт один из транзисторов VT1, VT2 или VT3, образующих динамическую нагрузку, и на выход F с шины питания поступает высокий потенциал, соответствующий лог. «1».

Трёхвходовый троичный логический элемент «3И–НЕ» выполняется схемотехнически следуя такой же логике. Выходной каскад его повторяет схемотехнику двоичного элемента «3И–НЕ», но на КМОП–транзисторах обогащенного типа с высоким пороговым напряжением. Ключ на КМОП–транзисторах с встроенным каналом также повторяет топологию двоичного элемента «3И–НЕ», как это показано на схеме ниже.

МОП–транзисторы T1, T2 и T3, включенные параллельно, здесь также образуют динамическую нагрузку, для комплементарных им МОП–транзисторов T4, T5 и T6, включенных последовательно с транзисторами динамической нагрузки. Транзисторы T4, T5 и T6, включенные последовательно, в этом случае коммутируют на выход Y низкий потенциал источника питания отрицательной полярности, соответствующий лог. «–1». Затворы транзисторов T1, T2 и T3 соединены попарно с затворами транзисторов T4, T5 и T6, соответственно, образуя входы A, B и C троичного логического элемента. Транзисторы T1 и T4, T2 и T5, T3 и T6, работают в противофазе с троичными сигналами лог. «1» и лог. «–1», при этом включенные последовательно транзисторы T4, T5 и T6 фактически реализуют логику элемента «3И–НЕ» для этих уровней. Когда на их затворах одновременно присутствует высокий уровень лог. «1», эти транзисторы открыты, и на выход Y поступает низкий потенциал источника питания отрицательной полярности, соответствующий лог. «–1». Транзисторы T1, T2 и T3 при этом все одновременно закрыты.

Отличие данной схемы троичного логического элемента «3И–НЕ» заключается в том, что пары транзисторов T1 и T4, T2 и T5, T3 и T6 могут быть закрыты одновременно и попарно, если на их затворах присутствует потенциал общего провода, соответствующий в данном случае лог. «0».

МОП–транзисторы T7, T8, T9, T10, T11 и T12 образуют ключ, коммутирующий на выход Y потенциал общего провода, при этом T10, T11 и T12 включены параллельно, а T7, T8, T9 — последовательно с ними. Все эти транзисторы имеют встроенный канал и при нулевом потенциале на затворах нормально открыты. При этом они соединены затворами попарно и подключены ими к входам A, B и C троичного логического элемента.

Исходя из такого построения, ключ на этих транзисторах сможет подать на выход Y потенциал общего провода однозначно в том случае, когда на всех затворах транзисторов присутствует потенциал лог. «0», поскольку в этом случае выключены транзисторы T1 и T4, T2 и T5, T3 и T6.

МОП–транзисторы T7, T8, T9 остаются включенными, когда на их затворы подаётся сигнал лог. «0» или лог. «1», в этом случае потенциал общего провода может быть подан на выход Y в том случае, когда на входах A, B и C присутствует хотя бы один или два лог. «0».

Если же хотя бы на одном из входов A, B или C присутствует сигнал лог. «–1», то цепочка МОП–транзисторов T7, T8, T9, однозначно выключена, и сигнал лог. «0» на выход Y не может быть подан.

Исходя из изложенных выше соображений, таблица истинности троичного логического элемента «3И–НЕ» имеет следующий вид.

Проанализировав таблицу, можно сформулировать следующие правила для троичной конъюнкции, которые можно распространить на любое число аргументов.

Троичная конъюнкция имеет следующие значения истинности:

1) она верна, когда все аргументы верны;

2) она ложна, когда ложен, по крайней мере, один из аргументов (каково бы ни было в это время значение остальных);

3) она определена только в этих случаях (и не определена, во всех остальных).

Из таблицы также следует, что на выход троичного логического элемента «3И–НЕ» всегда проходит меньшее из всех значений на его входах, и поэтому в троичной логике этот элемент принято называть «3INV–MIN».

Следует подчеркнуть, что это свойство справедливо при любом количестве входных аргументов.

На осциллограммах ниже показаны сигналы на входе C элемента «3INV–MIN» (красный, пилообразный, частотой 100 кГц) и на выходе Y (синий). На входы A и B элемента подан сигнал лог. «1» через резистор номиналом 1 кОм с шины питания +6 В.

Очевидно, что троичный логический элемент «3INV–MIN» по уровню, соответствующему троичной лог. «1», поданному на два из трёх входов, с точностью до инверсии прозрачен для любых троичных входных сигналов на третьем входе.

Модель троичного логического элемента «3INV–MIN», также была оформлена в виде отдельного функционального модуля, который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Представленный на рисунке выше модуль фактически является троичным аналогом двоичного логического элемента, изображенного на рисунке ниже.

Понятно, что по принципам, подробно разобранным выше, можно строить троичные логические элементы «INV–MIN» и с большим числом входов, добавляя МОП–транзисторы соответствующих типов в последовательные и параллельные группы устройства и объединяя их затворы.

Прежде чем перейти к обсуждению схемотехники элементов троичной дизъюнкции, обратим внимание на тот факт, как явно схемотехника двоичных логических КМОП–элементов иллюстрирует правила де Моргана.

На рисунках ниже изображены двоичный логический элемент «И–НЕ» (слева) и двоичный логический элемент «ИЛИ–НЕ» (справа).

|

|

У элемента «И–НЕ» МОП–ключи, определяющие логику работы, включены последовательно, в то время как МОП–транзисторы активной нагрузки — параллельно. Поэтому для сигналов высокого уровня должен быть включен первый «И» второй ключ. Элемент «И–НЕ» эксклюзивно реагирует на совпадение сигналов высокого уровня (лог. «1»). Но для сигналов низкого уровня (лог. «0») этот элемент фактически выполняет функцию «ИЛИ» — нижние ключи не включены одновременно, следовательно, включается «ИЛИ» один МОП–транзистор активной нагрузки, «ИЛИ» другой, «ИЛИ» оба вместе.

Обратив теперь внимание на схемотехнику элемента «ИЛИ–НЕ» справа, подчеркнём, что это фактически перевёрнутый элемент «И–НЕ», типы транзисторов в котором заменены на комплементарные.

МОП–ключи, определяющие логику работы элемента, включены параллельно, а МОП–транзисторы активной нагрузки — последовательно. Поэтому элемент «ИЛИ–НЕ» эксклюзивно реагирует на совпадение сигналов низкого уровня (лог. «0»). При этом включаются одновременно оба МОП–транзистора активной нагрузки, соединённые последовательно, в то время как ключи, определяющие логику работы, оба выключены. То есть, для сигналов низкого уровня (лог. «0») этот элемент работает как «И–НЕ», а по сигналам высокого уровня (лог. «1») транзисторы активной нагрузки одновременно не включаются, в то же время включается «ИЛИ» один нижний логический ключ, «ИЛИ» другой, «ИЛИ» оба вместе.

Понимание такой глубокой взаимной симметрии логических элементов «И–НЕ» и «ИЛИ–НЕ», которую, собственно, и декларируют правила де Моргана, окажется весьма полезным при обсуждении схемотехнических решений, характерных для элементов троичной дизъюнкции.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download