Логические элементы троичной дизъюнкци ("MAX","ИЛИ")

Распространённое определение дизъюнкции формулируется следующим образом.

Дизъюнкция — логическая операция, действие которой по смыслу максимально приближенно к реализуемому союзом "или" в смысле "или то, или это, или оба сразу". Синонимы: логическое "ИЛИ", включающее "ИЛИ", логическое сложение, иногда просто "ИЛИ". Дизъюнкция может быть бинарной операцией, тернарной (троичной) операцией, или n–арной операцией.

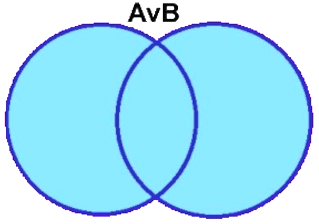

В графическом представлении результатом этой операции является объединение двух или более множеств.

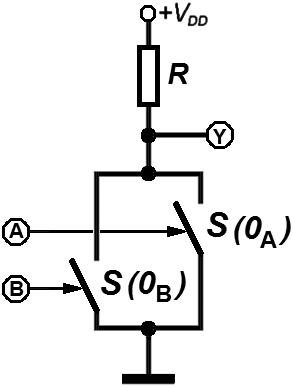

Простейшая контактная электрическая схема, реализующая операцию дизъюнкции, выглядит следующим образом.

Через резистор R будет проходить ток, а, следовательно, на выходе Y появится потенциал низкого уровня, если, согласно воздействиям на входах A и B, будет замкнут ключ S(0A) «ИЛИ» ключ S(0B) «ИЛИ» оба ключа одновременно. Если ни один из этих ключей не замкнут, ток через резистор R не проходит, и на выходе Y удерживается потенциал высокого уровня. Следуя этой логике, если воспринимать замыкание ключей сигналами на входах A и B как события истинные (лог. «1»), то представленная на рисунке выше электрическая цепь реализует логическую операцию инверсии дизъюнкции двух входных аргументов, иначе говоря, функцию «ИЛИ–НЕ» (NOR – Not OR).

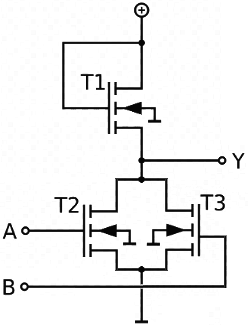

По такому принципу была построена схемотехника логических элементов на ранних этапах МОП–технологии. Ниже представлена схема логического элемента «ИЛИ–НЕ», выполненного по технологии N–МОП (NMOS).

В качестве резистора нагрузки R в N–МОП (или P–МОП) технологии применяется стабилизатор тока на транзисторе T1. Этот транзистор имеет индуцированный канал, и представляет собой фактически аналог резистора с большим динамическим сопротивлением. N–МОП транзисторы T2 и T3, включенные параллельно, играют роль ключей S(0A) и S(0B), соответственно.

Основным недостатком логических элементов, выполненных по N–МОП (или P–МОП) технологии: является бесполезное потребление энергии от источника питания в состоянии лог. «0» на выходе. Логические элементы, выполненные по технологии КМОП, этого недостатка лишены.

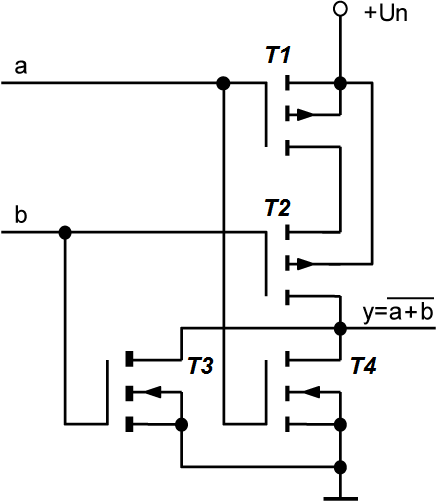

Принцип построения логического элемента «ИЛИ–НЕ» по технологии КМОП, можно продемонстрировать на основе следующей ключевой схемы.

Как видно из рисунка выше, каждый из ключей S(0A) и S(0B), соединённых параллельно, способен коммутировать низкий потенциал лог. «0» на выход Y. Эти ключи, собственно, и реализуют логику операции «ИЛИ». Ключи же S(1A) и S(1B) соединены последовательно, работают в противофазе ключам S(0A) и S(0B), и образуют для них так называемую динамическую нагрузку.

Если, согласно воздействиям на входах A и B, какой-либо из ключей S(0A) и S(0B) будет замкнут (либо оба ключа одновременно), то какой-либо из ключей S(1A) и S(1B) будет разомкнут, либо оба одновременно. В результате на выход Y, поступит низкий потенциал лог. «0». Если же оба ключа S(0A) и S(0B) не замкнуты, то обязательно замкнуты оба ключа S(1A) и S(1B). Следовательно, через них, на выход Y подаётся потенциал высокого уровня, соответствующий лог. «1». Так реализуется логика работы элемента «ИЛИ–НЕ» по технологии КМОП — на выходе Y низкий потенциал лог. «0», если замкнут ключ S(0A) «ИЛИ» ключ S(0B), «ИЛИ» замкнуты оба ключа одновременно. Схема элемента на КМОП–транзисторах, представленная ниже, полностью реализует схемотехнически это качественное описание с помощью ключей.

Имея опыт создания троичного КМОП–вентиля, аналога двоичного логического элемента «И–НЕ», по индукции можно с достаточной уверенностью предположить, что КМОП–транзисторы T1 и T2 в схеме троичного КМОП–вентиля «ИЛИ–НЕ» будут выполнять аналогичную функцию — коммутировать на выход Y высокий потенциал, соответствующий лог. «1». КМОП–транзисторы T3 и T4 также будут выполнять в схеме характерную для них функцию — коммутировать на выход Y низкий потенциал, но в троичной логике он соответствует лог. «–1». Пороги включения этих транзисторов будут увеличены, также как это было сделано в схеме троичного КМОП–вентиля «INV–MIN».

Из факта совместимости троичной логики с двоичной по логическим уровням, соответствующим понятиям «ИСТИННО» и «ЛОЖНО» о принципах работы этих транзисторов можно сделать следующий вывод.

Если включены оба КМОП–транзистора T1 и T2, то непременно должны быть выключены транзисторы T3 и T4, и на выход Y поступает высокий потенциал, соответствующий лог. «1». В этом случае дополнительные транзисторы ключа, коммутирующего на выход Y потенциал, соответствующий лог. «0» троичной логики также должны быть выключены.

Если включены один или оба МОП–транзистора T3 и T4, то из транзисторов T1 и T2 должен быть выключен хотя бы один или оба одновременно, следовательно, на выход Y поступает низкий потенциал, соответствующий лог. «–1». И в этом случае дополнительные транзисторы ключа, коммутирующего на выход Y потенциал, соответствующий лог. «0» троичной логики также должны быть выключены. То есть, когда транзисторы T1, T2, T3 и T4, работают с логическим уровням, соответствующим понятиям «ИСТИННО» и «ЛОЖНО», дополнительные транзисторы бездействуют.

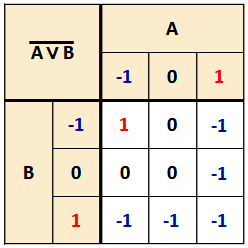

Чтобы понять, как они должны работать в том случае, когда на входе появляется логический уровень, соответствующий понятию «НЕИЗВЕСТНО», рассмотрим две части таблицы истинности, выделенные на рисунке Троичное «MAX» красным и синим контурами.

Внимательно проанализировав их, можно увидеть, что и та и другая соответствую таблице истинности для двоичного элемента «ИЛИ», но в таблице, выделенной синим контуром в роли понятия «ЛОЖНО» выступает лог. «–1» троичной логики, тогда как понятию «ИСТИННО» соответствует лог. «0». В таблице же, выделенной красным контуром, лог. «0» выступает как раз в роли понятия «ЛОЖНО», в то время как «ИСТИННО» — лог. «1». Это явно подсказывает, какой должна быть схемотехника ключа, коммутирующего на выход Y потенциал, соответствующий лог. «0» троичной логики в троичном вентиле «ИЛИ–НЕ»: она должна быть полностью аналогична топологии этого ключа в схеме троичного элемента «INV–MIN», но типы каналов МОП–транзисторов должны измениться на взаимно комплементарные.

Иными словами, если в схеме троичного элемента «INV–MIN», транзисторы МОП–транзисторы со встроенным каналом P–типа были включены параллельно, а последовательно с ними были включены транзисторы со встроенным каналом N–типа, то в схеме троичного элемента «INV–MAX» параллельно включаются МОП–транзисторы со встроенным каналом N–типа, тогда как транзисторы со встроенным каналом P–типа включаются последовательно с ними.

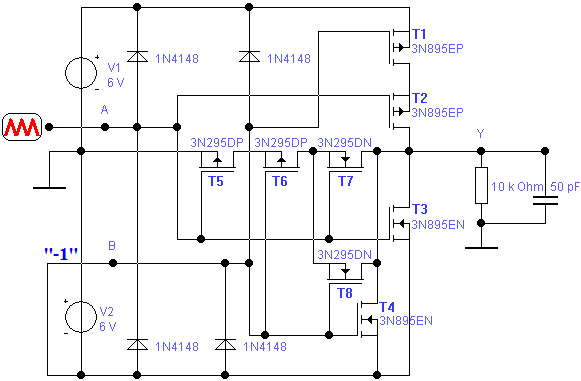

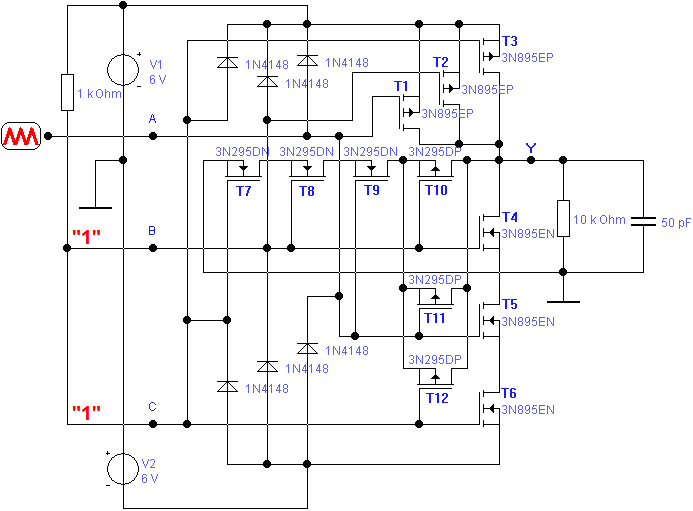

Схема электрическая принципиальная троичного логического элемента «INV–MAX» представлена на рисунке ниже.

На схеме выше красным контуром выделена часть схемы, которая фактически выполняет операцию двоичного «ИЛИ–НЕ» с троичными логическими уровнями, соответствующими понятиям «ИСТИННО» и «ЛОЖНО». Синим контуром выделена практически идентичная ей по топологии часть схемы, выполняющая фактически операцию двоичного «ИЛИ–НЕ» с троичными логическими уровнями, соответствующими понятиям «ИСТИННО»–«НЕИЗВЕСТНО», а также с «НЕИЗВЕСТНО»–«ЛОЖНО».

То есть, в то время, когда идёт работа троичного логического элемента «INV–MAX» с логическими уровнями «ИСТИННО» и «ЛОЖНО», работает часть схемы, выделенная красным контуром. Часть схемы, выделенная синим контуром, в это время заблокирована входными сигналами. Если же на входе троичного логического элемента «INV–MAX» появляется сигнал «НЕИЗВЕСТНО», то часть схемы, выделенная синим контуром, выполняет функцию двоичного «ИЛИ–НЕ» либо с транзисторами T1 и T2, из красного контура, либо же с транзисторы T3 и T4.

Так, собственно, схема троичного логического элемента «INV–MAX» реализует логическую операцию инверсии дизъюнкции: на выход троичного логического вентиля «INV–MAX» проходит с инверсией максимальный из двух входных сигналов. По уровню, соответствующему троичной лог. «–1» на одном из входов, вентиль «INV–MAX» прозрачен для любых троичных входных сигналов на другом входе. По уровню, соответствующему троичному лог. «0», вентиль «INV–MAX» прозрачен для троичного сигнала лог. «1». По уровню, соответствующему троичному лог. «–1» на одном из входов, вентиль «INV–MAX» непрозрачен для любых входных сигналов.

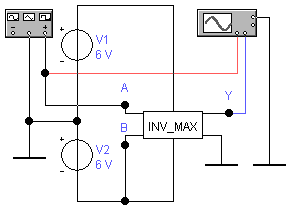

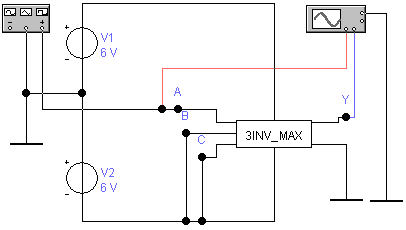

Ниже представлена модель троичного логического элемента «INV–MAX», выполненная в программе схемотехнического моделирования.

На входах схемы подключены защитные диоды, которые при моделировании привносят свой вклад во входную ёмкость модели троичного логического элемента «INV–MAX».

Схема включает в себя два источника напряжения V1 и V2, которые обеспечивают симметричное питание ±6 В, а также КМОП–транзисторы, образующие, как это рассматривалось ранее, "ключи", коммутирующие на выход схемы Y либо положительную шину питания (+6 В), либо потенциал общего провода ("земли"), либо отрицательную шину питания (–6 В), в зависимости от комбинации входных сигналов А и B.

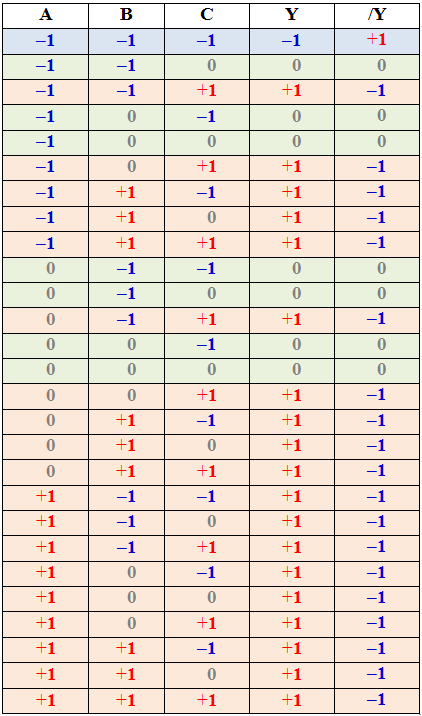

Таблица истинности исследуемой модели троичного логического элемента «INV–MAX» приведена ниже.

Рассмотрим результаты моделирования троичного логического элемента «INV–MAX».

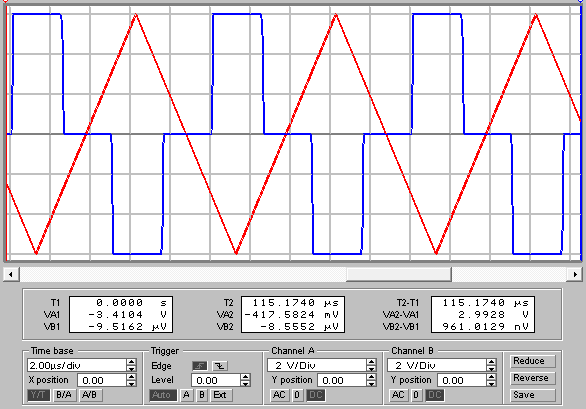

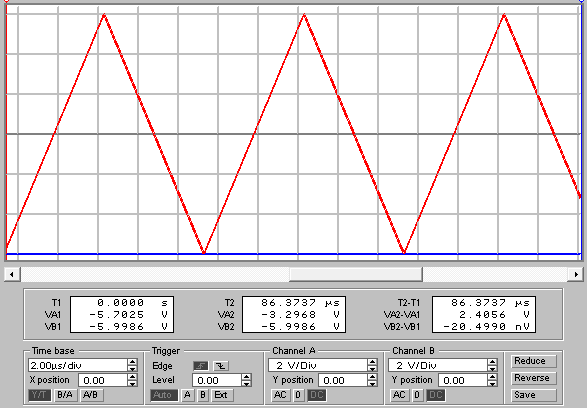

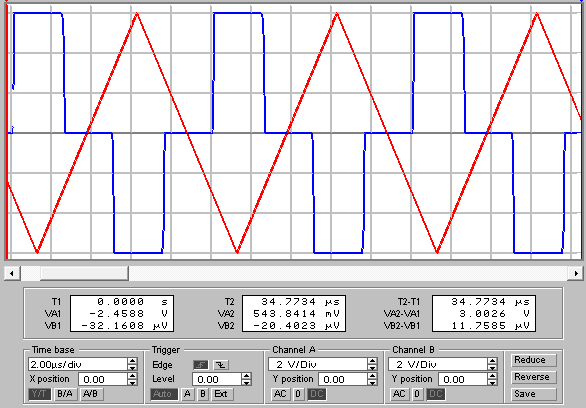

На рисунке ниже приведены осциллограммы входного пилообразного сигнала (красный цвет) частотой 100 кГц, поданного на вход A, и выходного сигнала троичного логического элемента «INV–MAX» (синий цвет) при работе на нагрузку 10 кОм, 50 пФ. На вход B вентиля при этом подан потенциал лог. «–1» с шины отрицательного потенциала источника V2.

Очевидно, что модель троичного логического элемента «INV–MAX» демонстрирует полное соответствие своей таблице истинности. По уровню, соответствующему троичной лог. «–1» на одном из входов, вентиль «INV–MAX» с точностью до инверсии прозрачен для любых троичных входных сигналов на другом входе.

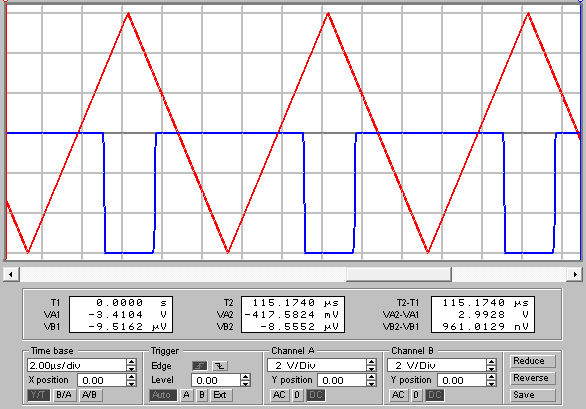

Далее приведены осциллограммы входного пилообразного сигнала (красный цвет) частотой 100 кГц, поданного на вход A, и выходного сигнала троичного логического элемента «INV–MAX» (синий цвет) при работе на нагрузку 10 кОм, 50 пФ. На вход B вентиля при этом непосредственно подан сигнал лог. «0» с общей шины питания.

Очевидно, что по уровню, соответствующему троичному лог. «0» на одном из входов, вентиль «INV–MAX» с точностью до инверсии прозрачен лишь для троичного сигнала лог. «1» на другом входе.

Следующий рисунок иллюстрирует тот факт, что по уровню, соответствующему троичному лог. «1» на одном из входов, вентиль «INV–MAX» ни для каких входных сигналов не прозрачен.

Модель троичного логического элемента «INV–MAX» была оформлена в виде отдельного функционального модуля, который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

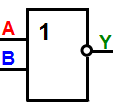

Представленный на рисунке выше функциональный модуль «INV–MAX», фактически является троичным аналогом двоичного логического элемента, изображенного на рисунке ниже.

Возможность замены P–канального МОП–транзистора со встроенным каналом на P–канальный полевой транзистор с изоляцией затвора p-n–переходом на модели троичного логического элемента «INV–MAX» не проверялась, поскольку эксперименты, проведённые ранее с моделями троичного логического элемента «INV–MIN» и троичного инвертора уверенно подтвердили работоспособность такого схемотехнического решения.

Трёхвходовый троичный логический элемент «3ИЛИ–НЕ» выполняется схемотехнически, следуя по индукции тем же решениям, на основе которых был разработан троичный логический элемент «INV–MAX». Выходной каскад его повторяет схемотехнику двоичного элемента «3ИЛИ–НЕ», но на КМОП–транзисторах обогащенного типа с высоким пороговым напряжением. Ключ на КМОП–транзисторах с встроенным каналом также повторяет топологию двоичного элемента «3ИЛИ–НЕ», как это показано на схеме ниже.

МОП–транзисторы T1, T2 и T3, включенные последовательно, образуют здесь динамическую нагрузку, для соединенных параллельно комплементарных им МОП–транзисторов T4, T5 и T6, включенных последовательно с транзисторами динамической нагрузки. Транзисторы T4, T5 и T6, соединенные параллельно, способны каждый индивидуально коммутировать на выход Y низкий потенциал источника питания отрицательной полярности, соответствующий лог. «–1». Включенные последовательно МОП–транзисторы T1, T2 и T3 способны коммутировать на выход Y высокий потенциал источника питания положительной полярности лишь в том случае, когда они включены все одновременно. Затворы транзисторов T1, T2 и T3 соединены попарно с затворами транзисторов T4, T5 и T6, соответственно, образуя входы A, B и C троичного логического элемента. Транзисторы T1 и T4, T2 и T5, T3 и T6, работают в противофазе с троичными сигналами лог. «–1» и лог. «1», при этом включенные параллельно транзисторы T4, T5 и T6 фактически реализуют логику элемента «3ИЛИ–НЕ» для этих уровней. Когда хотя бы на одном из их затворов присутствует высокий уровень лог. «1», соответствующий транзистор открыт, и на выход Y поступает низкий потенциал источника питания отрицательной полярности, соответствующий лог. «–1». Транзисторы T1, T2 и T3 включены последовательно, и если хотя бы один из них закрыт, то вся цепочка не способна подать на выход Y высокий потенциал источника питания положительной полярности, соответствующий лог. «1».

Пары транзисторов T1 и T4, T2 и T5, T3 и T6 могут быть закрыты как одновременно, так и попарно, если на их затворах присутствует потенциал общего провода, соответствующий в данном случае лог. «0».

МОП–транзисторы T7, T8, T9, T10, T11 и T12 образуют ключ, коммутирующий на выход Y потенциал общего провода, при этом T10, T11 и T12 включены параллельно, а T7, T8, T9 — последовательно с ними. Все эти транзисторы имеют встроенный канал и при нулевом потенциале на затворах нормально открыты. При этом они соединены затворами попарно и подключены ими к входам A, B и C троичного логического элемента.

Исходя из такого построения, ключ на этих транзисторах сможет подать на выход Y потенциал общего провода однозначно в том случае, когда на всех затворах транзисторов присутствует потенциал лог. «0», поскольку в этом случае выключены транзисторы T1 и T4, T2 и T5, T3 и T6.

МОП–транзисторы T7, T8, T9 остаются включенными, когда на их затворы подаётся сигнал лог. «0» или лог. «–1». В этом случае потенциал общего провода (лог. «0») может быть подан на выход Y в том случае, когда на входах A, B и C присутствует хотя бы один или два лог. «0», удерживающих открытыми один или два из транзисторов T10, T11, T12.

Если же хотя бы на одном из входов A, B или C присутствует сигнал лог. «1», то цепочка МОП–транзисторов T7, T8, T9, однозначно выключена, и сигнал лог. «0» на выход Y не может быть подан.

Таблица истинности троичного логического элемента «3ИЛИ–НЕ» имеет следующий вид.

Проанализировав таблицу, можно сформулировать следующие правила для троичной дизъюнкции, которые можно распространить на любое число аргументов.

Троичная дизъюнкция имеет следующие значения истинности:

1) она верна, когда верен хотя бы один из аргументов (каково бы ни было в это время значение остальных);

2) она ложна, когда все аргументы ложны;

3) она определена только в этих случаях (и не определена, во всех остальных).

Из таблицы также следует, что на выход троичного логического элемента «3ИЛИ–НЕ» всегда проходит большее из всех значений на его входах, и поэтому в троичной логике этот элемент принято называть «3INV–MAX».

Следует подчеркнуть, что это свойство справедливо при любом количестве входных аргументов.

На осциллограммах ниже показаны сигналы на входе A элемента «3INV–MAX» (красный, пилообразный, частотой 100 кГц) и на выходе Y (синий). На входы B и C элемента подан сигнал лог. «–1» непосредственно с шины питания –6 В.

Очевидно, что троичный логический элемент «3INV–MAX» по уровню, соответствующему троичной лог. «–1», поданному на два из трёх входов, с точностью до инверсии прозрачен для любых троичных входных сигналов на его третьем входе.

Модель троичного логического элемента «3INV–MAX», также была оформлена в виде отдельного функционального модуля, который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Представленный на рисунке функциональный модуль «3INV–MAX», фактически является троичным аналогом двоичного логического элемента, изображенного на рисунке ниже.

Отметим, что по принципам, подробно разобранным выше, можно строить троичные логические элементы «INV–MAX» и с большим числом входов, добавляя МОП–транзисторы соответствующих типов в последовательные и параллельные группы устройства и объединяя их затворы.

В заключение необходимо подчеркнуть, что в троичной логике разработанные логические элементы INV–MIN», «INV–MAX» и троичный инвертор не образуют функционально полный логический базис, на основе которого можно реализовать любое, сколь угодно сложное троичное устройство.

Тем не менее, на их основе можно создавать вполне работоспособные троичные логические узлы, типичным примером которых можно назвать троичный логический элемент «исключающее ИЛИ», об устройстве которого пойдёт речь в следующей части.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download