Макетирование троичного КМОП–инвертора на дискретных компонентах

К сожалению, в связи с введенным режимом самоизоляции, объявленным в связи с пандемией, и временным разрывом международных торгово-хозяйственных связей пришлось отказаться от закупки необходимых МОП–транзисторов на одном из крупных зарубежных агрегаторов электронных компонентов и обратится к альтернативным схемотехническим решениям.

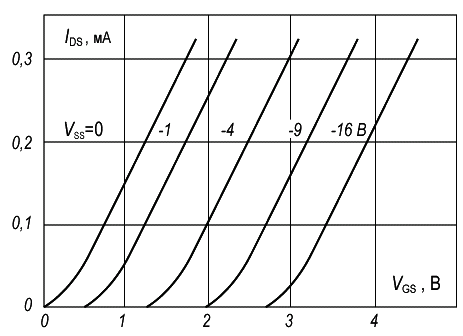

Известно [Xopoвиц П., Хилл У. Искусство схемотехники. Том 1, Москва: «Мир». 1986. с.371], что величину порогового напряжения МОП–транзистора можно изменять в довольно значительных пределах, подавая напряжение смещения на подложку.

Подача на подложку другого напряжения UПИ(ПОДЛОЖКА-ИСТОК) приводит к сдвигу порогового напряжения VTh на величину ΔVTh ≈ 0.5•UПИ в направлении, приводящем к уменьшению тока стока при данном напряжении затвора относительно истока UЗИ.

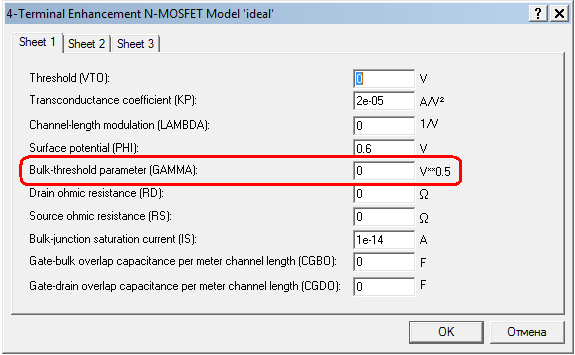

Модели МОП–транзисторов, используемые в программе схемотехнического моделирования, симуляцию эффекта смещения подложки поддерживают. За влияние подложки в них отвечает параметр Bulk threshold parameter GAMMA, который по умолчанию равен нулю.

Если эмпирически выставить значение этого безразмерного параметра в пределах 1...3, эффект смещения подложки симулируется.

На рисунке выше видно, что подача на подложку МОП–транзистора с пороговым напряжением VTh = 1 В напряжения смещения величиной –2 В приводит к изменению VTh на 1 В.

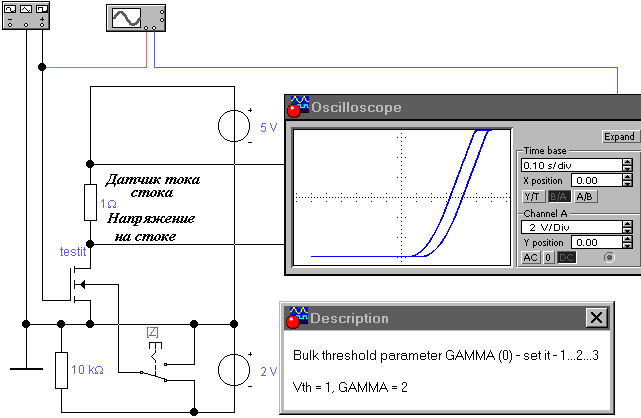

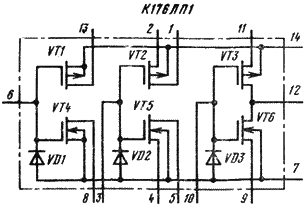

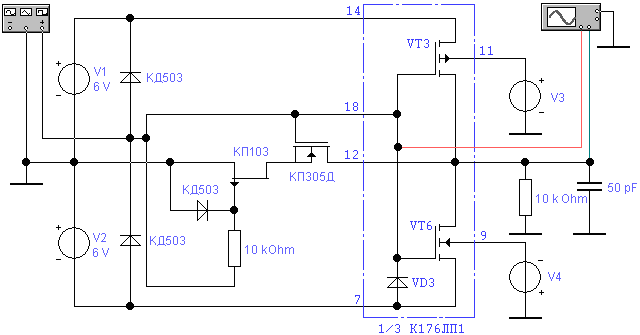

Эффект смещения подложки позволил при макетировании троичного инвертора использовать в качестве его выходных ключей S(1), S(–1), коммутирующих на нагрузку потенциалы напряжений питания, соответственно, +VDD и –VSS, интегральные транзисторы VT3, VT6 многоцелевой микросхемы К176ЛП1, представляющей собой фактически набор из трёх КМОП–транзисторов, коммутацию которых возможно в некоторых пределах осуществлять через внешние выводы микросхемы.

В качестве нормально открытого N–канального МОП–транзистора со встроенным каналом обеднённого типа для половины ключа S(0) хорошо подходит отечественный прибор типа КП305. В зависимости от исполнения, величина напряжения отсечки транзистора КП305 изменяется в довольно широких пределах (от –6 В до 1 В), что позволяет весьма несложно подобрать ему комплементарную пару.

К сожалению, нормально открытый P–канальный МОП–транзистор со встроенным каналом обеднённого типа отечественная электронная промышленность не выпускает. Но если сравнить сток–затворные характеристики P–канального МОП–транзистор со встроенным каналом и P–канального полевого транзистора с изоляцией затвора p-n–переходом

становится очевидно, что характеристика полевого транзистора с изоляцией затвора p-n–переходом (JFET — Junction-gate Field-Effect Transistor) очень похожа на характеристику МОП–транзистора.

Единственное отличие в том, что на затвор полевого транзистора с каналом P–типа и изоляцией p-n–переходом нельзя подавать отрицательное напряжение, поскольку это приведёт к открытию p-n–перехода. Но, как показал автор работы [Необычный режим работы полевого транзистора], при прямом смещении на затворе JFET в пределах 0,3…0,6 В, транзистор ещё сохраняет высокое входное сопротивление, и p-n–переход полностью не открыт.

Этот режим хорошо соответствует принципу работы ключа S(0) троичного инвертора: при достижении потенциала 0 В на затворе JFET будет полностью открыт, а при переходе в область отрицательных значений начнёт закрываться второй МОП–транзистор ключа. Следовательно, если ограничить отрицательное напряжение на затворе JFET, он вполне может сыграть столь необходимую роль P–канального МОП–транзистора со встроенным каналом обеднённого типа.

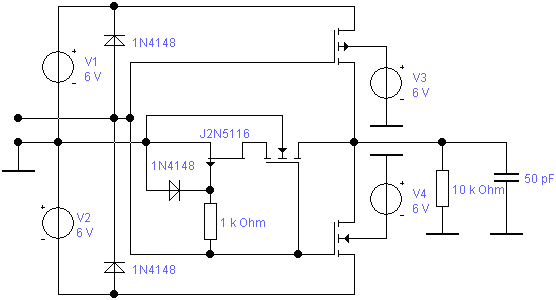

На рисунке ниже представлена схема макета троичного инвертора, включающего в свой состав полевой транзистор с изоляцией затвора p-n–переходом с ограничением отрицательного потенциала на затворе с помощью токоограничивающего резистора и диода, подключенного к затвору.

Полевой транзистор J2N5116 по большинству параметров не является явно комплементарным модели 3N295DN, а подбирался близким лишь по параметру напряжения отсечки из моделей реально существующих JFET. Этот параметр у транзистора J2N5116 составляет 2.73 В, тогда как напряжения отсечки у модели 3N295DN — –2.95 В.

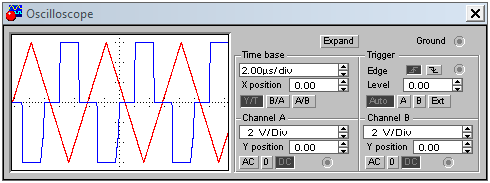

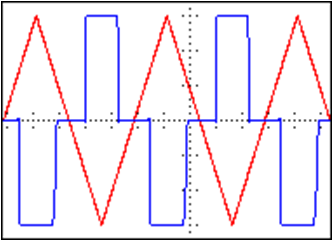

На рисунке ниже приведены осциллограммы работы модели троичного инвертора с полевым транзистором J2N5116 в качестве замены нормально открытого P–канального МОП–транзистора со встроенным каналом при частоте входного пилообразного сигнала 100 кГц.

Форма выходного сигнала незначительно искажена, транзистор J2N5116 с p-n–затвором затягивает фронт перехода от логической «–1» к «0», поскольку не является полностью комплементарным транзистору 3N295DN, имеет более низкое напряжение отсечки и меньшую крутизну. Но адекватность замены принципиально очевидна — выходной сигнал при работе на емкостную нагрузку 50 пФ и сопротивление 10 кОм соответствует исходной модели с нормально открытым P–канальным МОП–транзистором со встроенным каналом типа 3N295DP. Это позволяет использовать подобное схемотехническое решение при макетировании троичного инвертора.

В качестве отечественного аналога полевого транзистор J2N5116 вполне подходит P–канальный прибор с p-n–затвором типа КП103. В зависимости от индекса величина напряжения отсечки этого прибора изменяется также в довольно широких пределах (от 0,4 В до 7 В), даже при ограниченном количестве транзисторов подобрать пару для МОП–транзистора КП305 довольно несложно.

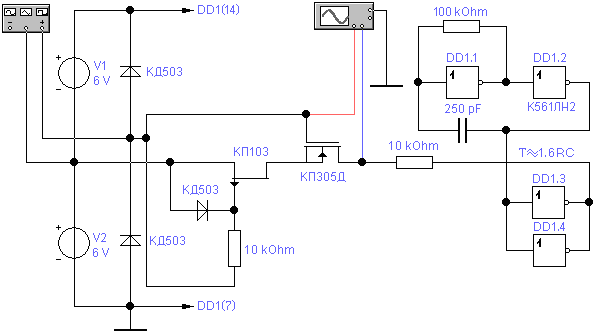

Поскольку под напряжением отсечки подразумевается такая величина напряжения затвор–исток, при которой ток канала уменьшается до фиксированного малого значения (обычно — 10 мкА), подбирать пару транзисторов с каналами P– и N–типов для построения троичного инвертора удобнее визуально — на экране осциллографа, собрав часть схемы инвертора, а именно, ключ S(0).

На макетной плате собирают вспомогательный генератор с частотой примерно 25 кГц для частоты входного пилообразного сигнала 1 кГц. Вспомогательный генератор выполняется на инверторах логической КМОП–микросхемы типа К561ЛН2 (или К561ЛА8) [Генераторы на КМОП логике]. Буферизированный выход генератора через резистор номиналом 10 кОм подключается к выводу ключа на полевых транзисторах. Пилообразный входной сигнал удобней инвертировать на входе осциллографа, если прибор позволяет инвертировать сигнал. В противном случае сигнал необходимо инвертировать на макетной плате с помощью каскада–инвертора, выполненного на операционном усилителе типа К140УД6 (К140УД12).

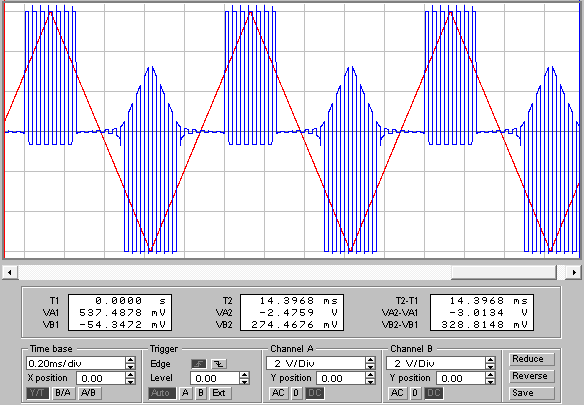

При подборе пары транзисторов наблюдается следующая осциллограмма.

Транзисторы подбираются таким образом, чтобы пересечение пилообразного сигнала с импульсным пакетом частотой 25 кГц приходилось примерно на середину амплитуды пилообразного сигнала или несколько меньше. Пакеты импульсов частотой 25 кГц должны быть примерно одинаковы по длительности.

После того как необходимая пара полевых транзисторы типов КП103 и КП305 подобрана, приступают отдельно к настройке выходного каскада — ключей S(1), S(–1), в качестве которых в схеме инвертора задействованы интегральные транзисторы VT3, VT6 многоцелевой микросхемы К176ЛП1. Пару транзисторов VT3, VT6 использовать предпочтительно, поскольку транзисторы с одинаковой проводимостью каналов соединены между собой как по цепям истоков, так и подложек. Но элементы VT1, VT2, VT4, VT5 не соединены стоками в пары, следовательно, при изменении, как питающего напряжения, так и смещения на подложках, эти транзисторы не смогут помешать корректной работе пары VT3, VT6.

Выставив номинальное напряжение питания ±6 В по цепям источников V1, V3 и V2, V4, и подав входной пилообразный сигнал амплитудой 6 В на вход A, медленно увеличивают смещение на подложках посредством регулировки источников V3, V4, наблюдая при этом осциллограмму на экране и добиваясь следующей её формы.

Интервалы логических уровней «–1», «0», «+1» должны быть примерно равны. Если не удаётся этого добиться, что происходит в тех случаях, когда пороговые напряжения полевых транзисторов VT3 и VT6 не получается значительно увеличить смещением на подложках, следует несколько уменьшить напряжения источников V1 и V2, после чего снова повторить подбор напряжений источников V3 и V4. Резистор номиналом в 10 кОм в этом случае служит в качестве подтягивающего к потенциалу логического «0», а после полной сборки троичного инвертора он возьмёт на себя роль пассивной нагрузки.

Итоговая сборка троичного инвертора после успешной настройки по частям заключается в соединении двух схем: ключа S(0) с цепями ключей S(1), S(–1).

Если предварительные настройки осуществлены правильно, на выходе троичного инвертора при подаче на вход пилообразного сигнала амплитудой 6 В наблюдается следующая осциллограмма.

Возможно, потребуется некоторая подстройка напряжения источников питания V1 и V2, и незначительный подбор напряжений смещения подложек регулировкой источников V3 и V4.

Таким образом, экспериментально подтверждена принципиальная возможность построения троичного инвертора на основе КМОП–транзисторных ключей с различными пороговыми напряжениями и напряжениями отсечки; продемонстрирована полная работоспособность транзисторного ключа на основе последовательно включенных нормально разомкнутых полевых транзисторов.

Следует также отметить, что макет троичного инвертора был выполнен полностью на доступных отечественных компонентах, что, несмотря на некоторые схемотехнические усложнения, позволяет успешно макетировать и более сложные узлы троичной логики. Но от привлекательной идеи выполнить макет троичного процессора на дискретных SMD компонентах по технологии поверхностного монтажа, как это сделал автор проекта [The MOnSter 6502], к сожалению, пришлось отказаться.

Схемотехническое решение по замене P–канального МОП–транзистора со встроенным каналом обеднённого типа на JFET усложняет схемотехнику троичного инвертора и несколько ухудшает его параметры, поскольку на одной полуволне управляющего сигнала он начинает потреблять от источника сигнала незначительный ток. Но, как показала практика, выходной каскад троичного инвертора вполне справляется с такой нагрузкой, а доступность P–канальных JFET упрощает макетирование и более сложных троичных устройств, в частности логических элементов троичной конъюнкции.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download