Полный одноразрядный троичный сумматор

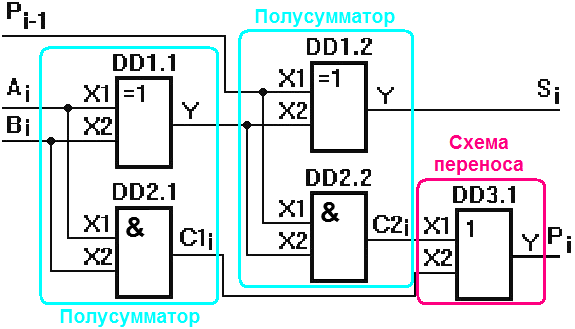

Если в качестве прототипа полного одноразрядного троичного сумматора придерживаться схемы его двоичного аналога:

то основной узел — троичный полусумматор, состоящий из троичного сумматора и схемы переноса, практически выполнен, и его модули успешно протестированы.

В двоичном полном одноразрядном сумматоре узел итогового переноса в старший разряд выполнен на логическом элементе «ИЛИ». Бит переноса в старший разряд формируется, если биты переноса генерируются на выходах первого или второго сумматоров или на выходах обоих одновременно. Как говорится «третьего не дано». В троичной цифровой технике это «третье» как раз присутствует, поэтому логика работы узла переноса в старший разряд несколько сложнее, хотя и во многом похожа.

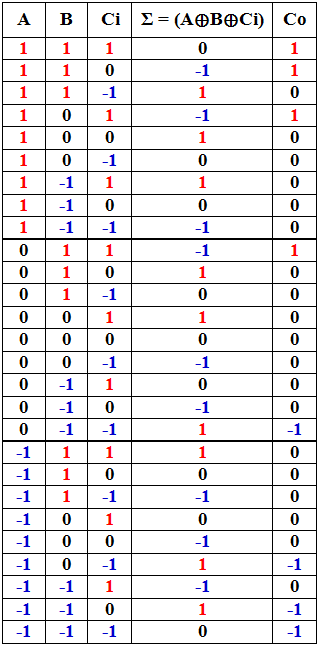

Перенос в троичном полном одноразрядном сумматоре возникает в следующих случаях:

- Если трит переноса на выходе одного из троичных полусумматоров равен «–1», а на выходе второго — «+1», и наоборот, то переноса в старший разряд на выходе полного сумматора нет, он равен «0».

- Если же трит переноса на выходе одного из полусумматоров равен «–1», а на выходе второго — «0» или «–1», то трит переноса в старший разряд на выходе полного сумматора равен «–1».

- Если трит переноса на выходе одного из полусумматоров равен «+1», а на выходе второго — «0» или «+1», то трит переноса в старший разряд на выходе полного сумматора равен «+1».

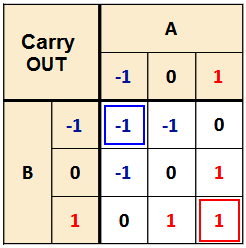

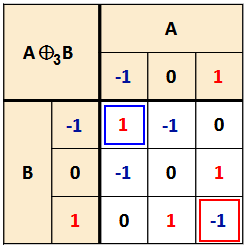

Таким образом, таблица истинности узла переноса в старший разряд полного троичного сумматора имеет следующий вид, представленный на рисунке ниже слева.

|

|

Перенос в старший разряд |

Сумма по модулю 3 |

Очевидно, что за исключением двух трит, выделенных цветным контуром, она практически полностью идентична таблице истинности сумматора по модулю 3.

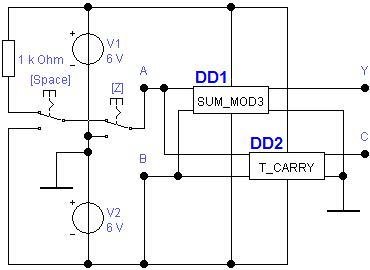

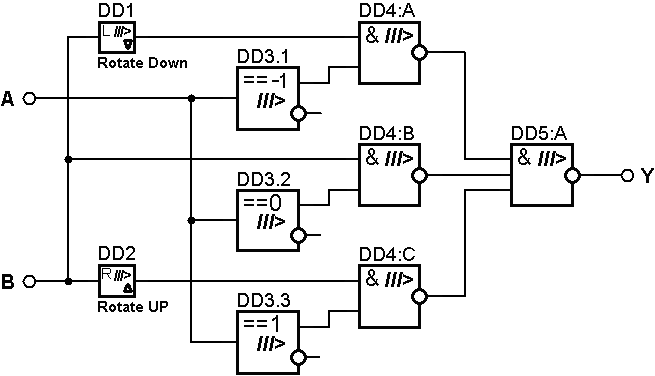

Если проанализировать схему сумматора по модулю 3, представленную на рисунке ниже:

очевидно, что за результат, отличающий друг от друга представленные выше таблица истинности, отвечают элементы правой и левой циклической инверсии. И чтобы достичь необходимого результата у элемента правой циклической инверсии необходимо исключить из функционала операцию лог. «+1» → лог. «–1». У элемента левой циклической инверсии в таком случае следует исключить операцию лог. «–1» → лог. «+1».

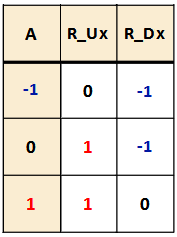

Таблицы истинности элементов правой и левой циклической инверсии в этом случае корректируются к следующему виду.

В троичной логике возможны 27 различных унарных функций, и функции, чьи таблицы представлены выше, — одни из них. Чтобы не изобретать для них отдельных названий, они именованы по своим прототипам с пометкой об исключении отдельной операции: «ROT_Ux» (ROTate Up with eXception — вращение вверх с исключением) и «ROT_Dx» (ROTate Down with eXception — вращение вниз с исключением).

Адаптация функций «ROT_UP» и «ROT_DN» к набору операций функций «ROT_Ux» и «ROT_Dx», приведённых в таблице выше, выразилась в коррекции их схемотехники удалением отдельных МОП–транзисторов.

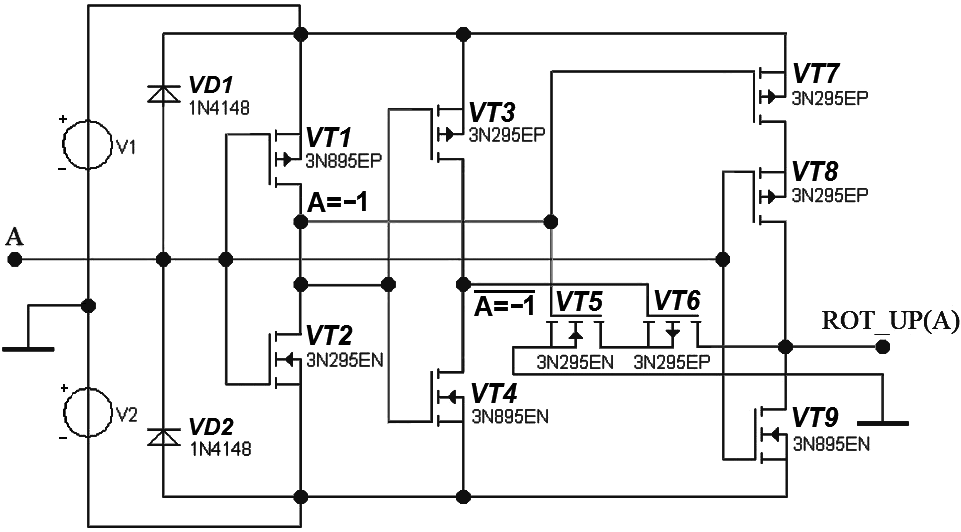

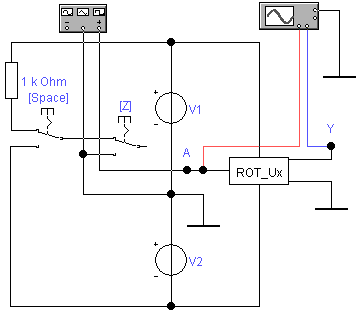

Так в схеме элемента правой циклической инверсии, представленной на рисунке ниже:

удалены МОП–транзисторы VT8, VT9. Итоговый вариант схемы «ROT_Ux» представлен на рисунке ниже.

Модель элемента «ROT_Ux» была оформлена в виде отдельного функционального модуля, который предназначен для использования в составе узла переноса в старший разряд полного троичного сумматора.

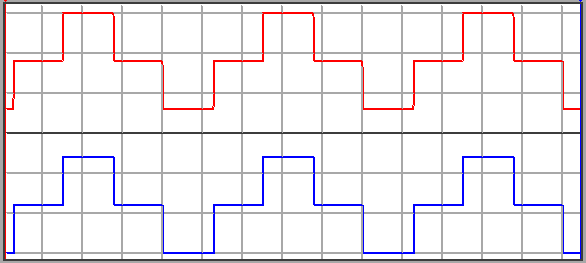

Осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A устройства, и выходного сигнала (синий цвет) элемента «ROT_Ux» приведены на рисунке ниже.

Осциллограммы подтверждают, что выходной сигнал Y (синий цвет) по отношению к входному пилообразному сигналу (красный цвет) изменяется по следующей закономерности: лог. «–1» → лог. «0», лог. «0» → лог. «+1», лог. «+1» → лог. «+1», что полностью соответствует требуемой логике работы троичного элемента «ROT_Ux» и его таблице истинности.

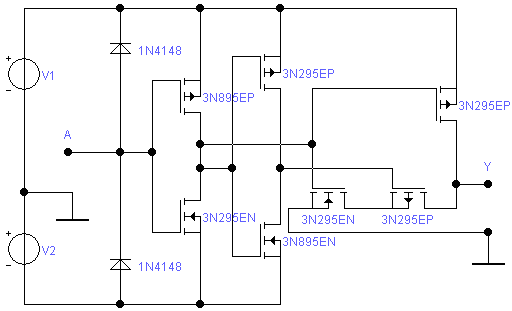

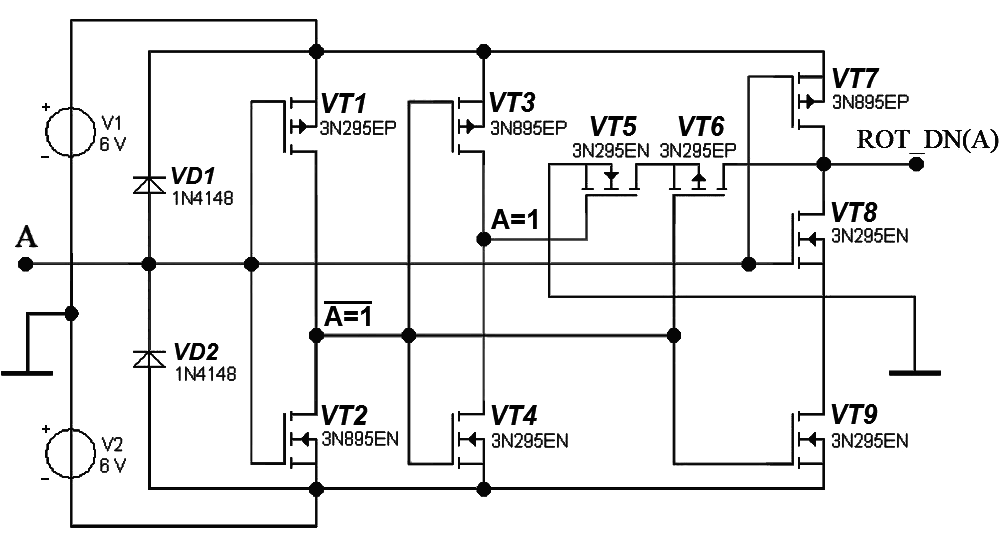

Исходная схема элемента левой циклической инверсии, представлена на рисунке ниже:

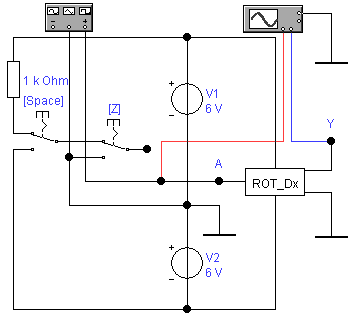

Из конструкции были удалены МОП–транзисторы VT7, VT8. Итоговый вариант схемы элемента «ROT_Dx» представлен на рисунке ниже.

Модель элемента «ROT_Dx» была оформлена в виде отдельного функционального модуля, который предназначен для использования в составе узла переноса в старший разряд полного троичного сумматора.

Осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A устройства, и выходного сигнала (синий цвет) элемента «ROT_Dx» приведены на рисунке ниже.

Осциллограммы подтверждают, что выходной сигнал Y (синий цвет) по отношению к входному пилообразному сигналу (красный цвет) изменяется по следующей закономерности: лог. «+1» → лог. «0», лог. «0» → лог. «–1», лог. «–1» → лог. «–1», что полностью соответствует требуемой логике работы троичного элемента «ROT_Dx» и его таблице истинности.

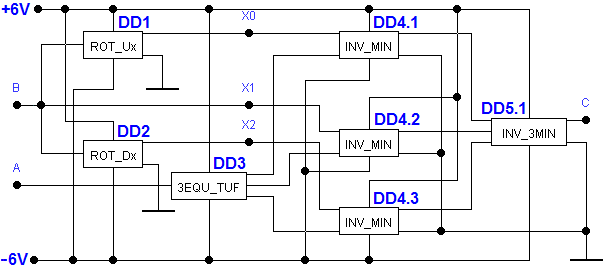

Модель узла переноса в старший разряд полного троичного сумматора с элементами «ROT_Ux» и «ROT_Dx» представлена на рисунке ниже.

С целью проверки работоспособности узла переноса в старший разряд на вход A устройства подавался трёхуровневый сигнал (красный цвет), полученный из пилообразного сигнала частотой 1 кГц, пропущенного через троичный вентиль. На вход B устройства последовательно выставлялись логические уровни «–1», «0», «+1».

Ниже представлены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) узла переноса в старший разряд при подаче вход B устройства логического уровня «–1».

Далее представлены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) узла переноса в старший разряд при подаче вход B устройства логического уровня «0».

На рисунке ниже приведены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) узла переноса в старший разряд при подаче вход B устройства логического уровня «+1».

Осциллограммы подтверждают работоспособность узла переноса в старший разряд, и соответствие выходных сигналов таблице истинности элемента Carry Out, приведенной ранее.

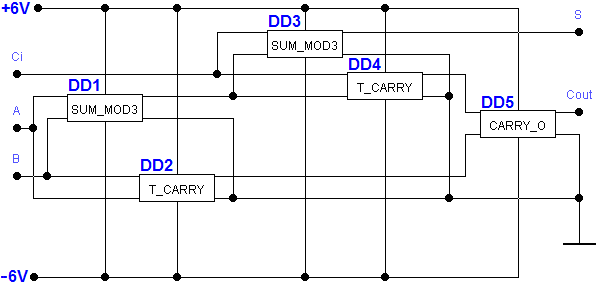

На основе проверенных и работоспособных узлов троичного полусумматора и переноса в старший разряд была создана модель полного троичного одноразрядного сумматора, представленная на рисунке ниже.

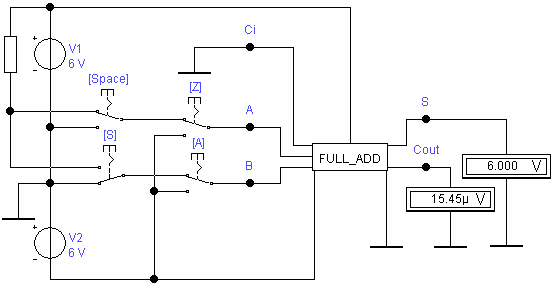

Для удобства исследования и измерения характеристик модель полного троичного одноразрядного сумматора была оформлена в виде законченного функционального модуля и снабжена коммутацией логических уровней на входах и индикацией на выходах, как это показано на рисунке ниже.

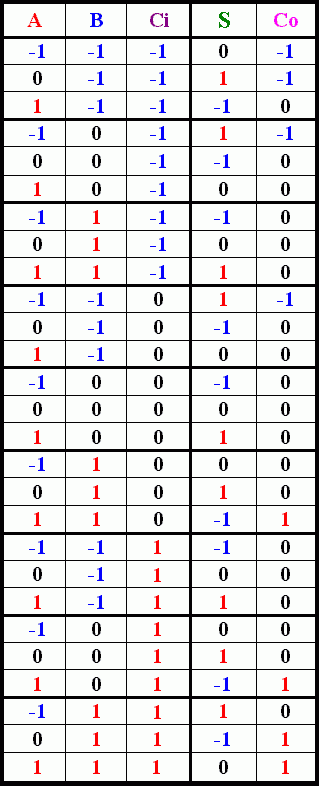

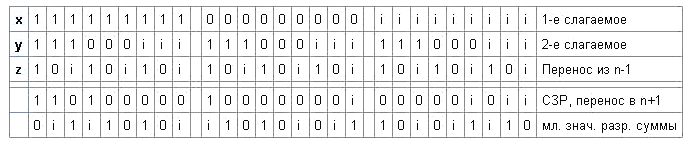

Ниже приведена таблица истинности полного одноразрядного троичного сумматора, измеренная на представленной выше модели.

Для удобства сравнения с известными результатами, опубликованными в открытых источниках, таблица истинности полного одноразрядного троичного сумматора была приведена к следующему виду.

Сравнение экспериментально измеренной таблицы истинности полного одноразрядного троичного сумматора с результатами, приведенными в сети Интернет [Троичные функции. Троичный симметричный сумматор–вычитатель], показало их полную идентичность.

Таким образом, продемонстрирована работоспособность модели полного одноразрядного троичного сумматора и возможность использования её при разработке троичного процессора.

Следует отметить, что модель полного одноразрядного троичного сумматора в рамках программы схемотехнического моделирования является аналоговой и содержит более 300 МОП–транзисторов. Поэтому при её исследовании и использовании следует подобрать разумный компромисс параметров численного интегрирования, чтобы помимо достаточной точности эмуляции иметь и приемлемую её скорость.

Необходимо также указать, что исследовать модель полного одноразрядного троичного сумматора, естественно, удобнее, подавая на её входы сигналы с выходов троичного счётчика.

О разработке троичных устройств последовательностного типа, и, в частности, троичного асинхронного триггера пойдёт речь в следующем разделе.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download