Троичный асинхронный RS-триггер

Все рассмотренные нами ранее троичные цифровые схемы относились к так называемым устройствам комбинационного типа, сигнал на выходе которых в определённый момент времени определяется лишь комбинацией логических сигналов на входах устройств в тот же самый момент времени.

Наряду с устройствами комбинационной логики в традиционной двоичной цифровой технике существует обширный класс цифровых устройств так называемого последовательностного типа.

Устройства такого типа это — цифровые автоматы и синхронные схемы, частным случаем которых является, собственно, процессор, но основное их свойство заключается в том, что подобные устройства обеспечивают «память» цифровых систем.

Основой для построения схем последовательностного типа в двоичной цифровой технике является асинхронный RS-триггер. И название последовательностных они получили по той причине, что сигнал на их выходе в определённый момент времени, определяется не только комбинацией логических сигналов на входах устройств в тот же самый момент времени, но и от предыдущего состояния сигналов на их выходах, то есть, от последовательности подачи сигналов на входы.

Триггером в двоичной цифровой технике принято называть логическое устройство последовательностного типа с обратными связями, обладающее двумя состояниями устойчивого равновесия (иначе говоря — бистабильная ячейка). Схема асинхронного RS–триггера на основе двоичных логических элементов «И-НЕ» представлена на рисунке ниже.

Триггер имеет два информационных входа: Set и Reset, и два выхода: Q и /Q. Он может быть установлен активным уровнем логического сигнала по входу Set, при этом на выходе Q устанавливается логическая «1», или сброшен по входу Reset, при этом на выходе Q — логический «0». Триггер такого типа называют асинхронным, поскольку он может быть установлен или сброшен в любой произвольный момент времени.

Прежде чем перейти к рассмотрению троичного триггера, прототипом которого является двоичный аналог, выделим для дальнейшего сравнения основные свойства двоичного триггера.

- Двоичный асинхронный RS-триггер при включении устанавливается в произвольное состояние.

- Выходы асинхронного RS-триггера Q и /Q. Всегда находятся в противофазном состоянии.

- Двоичный асинхронный RS-триггер, обладая двумя состояниями устойчивого равновесия «0» и «1», способен хранить 1 бит информации. Режиму хранения соответствует комбинация входных сигналов /S = «1», /R= «1».

- Будучи установленным активным уровнем сигнала по входу /Set или сброшенным — по входу /Reset, триггер не реагирует в дальнейшем на состояние этого управляющего входа и сохраняет свое состояние, пока не будет переключен активным уровнем по другому управляющему входу.

- Асинхронный RS-триггер имеет запрещенное состояние: /S = «0», /R= «0», при котором нарушается логика его работы, заключающаяся в том, что выходы триггера (прямой – Q и инверсный – /Q) всегда находятся в противофазе. Иначе говоря, подача на входы триггера одновременно сигналов /S = «0» и /R = «0», является невыполнимой попыткой заставить RS-триггер установиться в состояние лог. «1» и сброситься в лог. «0» одновременно.

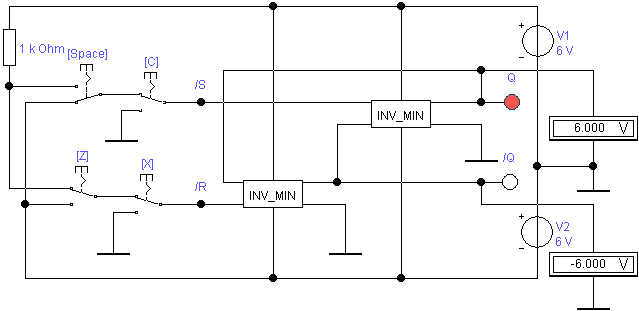

На основе двух троичных логических элементов «INV-MIN» — аналогов двоичных вентилей «И-НЕ» — в программе схемотехнического моделирования была реализована модель асинхронного троичного RS–триггера, представленная на рисунке ниже.

В неустоявшейся окончательно терминологии троичной логики это устройство называют «триттер», чтобы отличать от его двоичного аналога.

Поскольку элементы троичной логики обладают расширенным алфавитом по сравнению с их двоичными аналогами — «–1», «0», «+1» — логично обозначить переходы между состояниями RS-триттера следующим образом: переход в более низкое состояние — «сброс», переход в более высокое состояние — «установка».

Так переходы типа лог. «+1» → лог. «0», лог. «+1» → лог. «–1», лог. «0» → лог. «–1» — сброс в лог. «0» и лог. «–1», соответственно. Тогда как переходы типа лог. «–1» → лог. «0», лог. «0» → лог. «+1», лог. «–1» → лог. «+1» — установка в лог. «0» и лог. «–1».

С помощью модели, представленной на рисунке выше, была измерена таблица логических переходов RS–триттера.

Таблицу

Согласно представленным в таблице данным, можно сформулировать следующие свойства RS–триттера.

Активный низкий уровень напряжения (сигнал «–1») на входе /S осуществляет установку троичного RS–триттера, переход в состояние Q = 1, /Q = –1, при условии, что на входе /R сигнал логической «1».

Активный низкий уровень напряжения (сигнал «–1») на входе /R, осуществляет сброс троичного RS–триттера, переход в состояние Q = –1, Q = 1, при условии, что на входе /S сигнал логической «1».

Будучи установленным или сброшенным, RS–триттер не реагирует в дальнейшем на сигналы соответствующего управляющего входа и сохраняет свое состояние, пока не будет переключен по другому управляющему входу активным уровнем. Так же, как и двоичный прототип, RS–триттер хранит своё состояние при /S = 1, /R = 1.

Очевидно, что эти свойства характерны и для двоичного прототипа асинхронного RS–триттера. Но RS–триттер имеет и свои уникальные свойства, обусловленные логикой работы троичных вентилей «INV-MIN».

При включении RS–триттер устанавливается обычно в состояние «не определено» Q = 0, /Q = 0.

Будучи установленным, RS–триттер может быть сброшен в состояние неопределенности Q = 0, /Q = 0 только по входу /R логическим уровнем «0».

Будучи сброшенным, RS–триттер может быть установлен в состояние «не определено» Q = 0, /Q = 0 только по входу /S логическим уровнем «0».

Асинхронный RS–триттер имеет несколько запрещенных состояний при /S = –1, /R = –1; /S = –1, /R = 0; /S = 0, /R = –1; поскольку при этом нарушается логика его работы, предполагающая, что выходы Q и /Q всегда находятся в противофазе. Такие состояния неустойчивы.

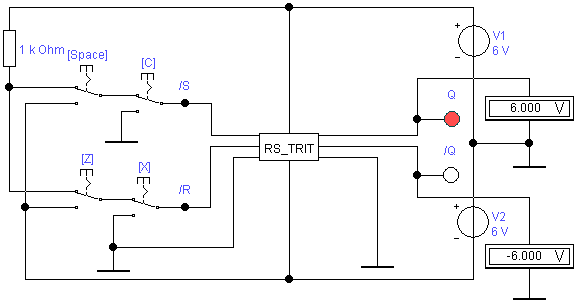

Для удобства применения в составе более сложных троичных цифровых систем модель асинхронного RS–триттера была оформлена в виде законченного функционального модуля, как это показано на рисунке ниже.

Таким образом, показано, что схемотехнически асинхронный троичный RS–триттер может быть реализован идентично двоичному RS–триггеру по схеме из двух логических вентилей «И» с инверсией и перекрёстными обратными связями.

На основе модели исследовано функционирование асинхронного RS–триттера, выявлены базовые принципы его работы и характерные особенности.

Асинхронный RS–триттер, безусловно, может претендовать на роль элементарной ячейки статической памяти в троичных цифровых системах. Тем не менее, асинхронный RS–триттер унаследовал от своего двоичного аналога такие неудобные с точки зрения схемотехники синхронных цифровых систем свойства, как асинхронность и наличие «запрещённого» состояния, при котором логика его работы нарушается. Для устранения этих свойств двоичного RS–триггера в его конструкцию на входы /S и /R обычно вводят вентили, прозрачные по активному сигналу «0» или «1». Подобное схемотехническое решение, известное в двоичной цифровой технике, логично применить и по отношению к троичной тристабильной ячейке, превращая её таким образом в синхронный RS–триттер.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download