Троичный полусумматор

(сумматор по модулю 3 и схема переноса)

При построении схемы полного троичного сумматора воспользуемся схемотехническими решениями, характерными для его двоичного аналога с учетом особенностей арифметики троичной симметричной (уравновешенной) системы счисления.

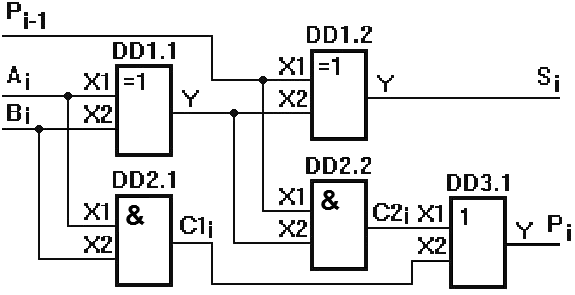

Схема электрическая принципиальная полного двоичного одноразрядного сумматора изображена на рисунке ниже.

На ней можно выделить узлы, характерные для построения полного сумматора: два сумматора по модулю 2 — DD1.1 и DD1.2. Первый из которых (DD1.1) вычисляет сумму по модулю 2 двух входных аргументов Ai и Bi, второй же (DD1.2) суммирует по модулю 2 полученный результат с битом переноса Pi-1 из предыдущего разряда, выдавая результат полной суммы с учетом флага переноса Si.

Два логических элемента «И» — DD2.1 и DD2.2 — как элементы, избирательно реагирующие на совпадение лог. «1», отслеживают переносы, возникающие как при сложении по модулю 2 самих входных аргументов Ai и Bi, так и при суммировании полученного результата с битом переноса Pi-1 из предыдущего разряда.

Фактически сумматор по модулю 2 DD1.1 и схема переноса DD2.1 образуют полусумматор. То же можно сказать про элементы DD1.2 и DD2.2.

Логический элемент DD3.1 формирует перенос в старший разряд, и в данном случае он придерживается логики «ИЛИ»: перенос возник на выходе элемента DD2.1 или на выходе DD2.2, или на обоих выходах вместе.

В двоичной логике функции сумматора по модулю 2 с успехом исполняет логический элемент «XOR», но, как было выяснено ранее, на роль сумматора по модулю 3 он не подходит, хотя и с успехом справляется с обязанностями троичного управляемого инвертора.

Для реализации схема переноса в троичной логике также вряд ли будет достаточно простого элемента «И», как в силу более обширного алфавита троичной логики, так и в силу особенностей троичной арифметики, на которые и обратим внимание.

Троичная симметричная (уравновешенная) система счисления (ТСС) в общем случае — позиционная система счисления по целочисленному основанию 3. Вариант симметричной системы подразумевает, что значения в ней могут быть отрицательными, нулевыми или положительными, другими словами –1, 0, +1.

Ключевая особенность троичной симметричной системы — наличие знака числа в самом её алфавите, т.е. знак числа однозначно определяется по самому числу без специального разряда знака. Если ведущий (старший) ненулевой разряд отрицателен, то и само число является отрицательным, в противном случае число положительно. Изменение знака числа производится инвертированием каждого разряда числа: положительный разряд меняется на отрицательный и наоборот, ноль остается без изменений.

Сложение в троичной симметричной системе производится по общим правилам для позиционных систем, но с учетом того, что в алфавите присутствуют отрицательные значения.

Так, к примеру, число 2 будет выражаться в этой системе как +1 (=3) в старшем разряде и –1 — в младшем разряде (3 – 1 = 2).

Число же –2 будет выглядеть как –1 (= –3) в старшем разряде и +1 — в младшем разряде (–3 + 1 = –2).

Рассмотрим результаты сложения в троичной симметричной системе в пределах одного разряда с учетом коммутативности этой операции.

|

–1 + (–1) = –1 – 1 = –2; |

в симметричной системе это: –3 + 1, откуда: +1 – в текущий разряд и –1 – перенос в старший |

|

–1 + 0 = –1 |

переноса нет, результат умещается в разряде |

|

–1 + 1 = –1 |

переноса нет, результат умещается в разряде |

|

0 + (–1) = 0 –1 = –1 |

переноса нет, результат умещается в разряде |

|

0 + 0 = 0 |

переноса нет, результат умещается в разряде |

|

0 + 1 = 1 |

переноса нет, результат умещается в разряде |

|

1 + (–1) = 1 – 1 = 0 |

переноса нет, результат умещается в разряде |

|

1 + 0 = 1 |

переноса нет, результат умещается в разряде |

|

1 + 1 = 2 |

в симметричной системе это: 3 – 1, откуда: –1 – в текущий разряд и 1 – перенос в старший |

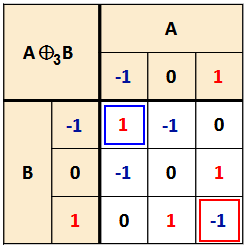

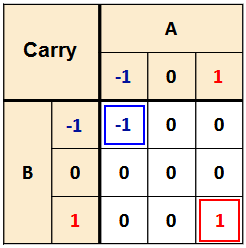

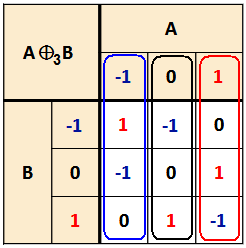

Исходя из приведенных выше результатов, можно сравнительно легко представить таблицы истинности как для троичного сумматора по модулю 3, так и для схемы переноса.

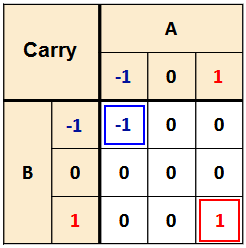

|

|

Таблица истинности троичного сумматора по модулю 3 |

Таблица истинности схемы переноса при суммировании по модулю 3 |

Для схемотехнической реализации троичного сумматора по модулю 3 вместо построения функции по таблице истинности и минимизации её воспользуемся известным из двоичной цифровой техники способом, который в ряде случаев приводит к довольно простым схемотехническим решениям.

В двоичной цифровой технике с помощью мультиплексора можно реализовать любую логическую функцию комбинационного типа с числом входных переменных, равных числу адресных входов мультиплексора, поскольку каждому адресу соответствует только один информационный вход. При этом схема работает фактически так же, как одноразрядное ПЗУ [Титце У., Шенк К. Полупроводниковая схемотехника (1980) Справочное руководство. С.327].

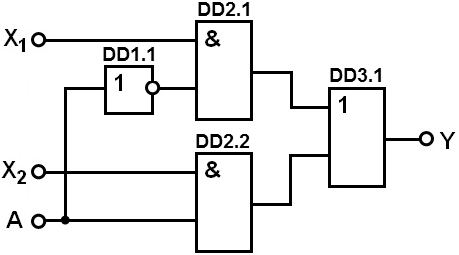

На рисунке ниже показано, как таким способом реализовать двоичный сумматор по модулю 2.

В работе [A.S. Kumar and A.S. Priya, Minimization of Ternary Combinational Circuits] показано, что такое схемотехническое решение вполне применимо и в троичной цифровой схемотехнике.

В двоичной цифровой схемотехнике мультиплексор – это устройство, подключающее единственный выходной канал к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом.

В самом простом случае двухвходовый мультиплексор реализует следующая схема.

В зависимости от значения (0, 1) на входе адресного сигнала A, на выход Y поступает значение X1 или X2.

На основе имеющейся элементной базы, троичный мультиплексор может быть выполнен схематически аналогично с учетом специфики троичного сигнала.

Декодеры троичных логических уровней «–1», «0», «+1» — DD1, DD2 и DD3 соответственно, при обнаружении соответствующего уровня, открывают активным уровнем «+1» на выходе соответствующие им вентили «INV-MIN» — DD4.1, DD4.2 или DD4.3. Трёхвходовый логический элемент «3INV-MIN» — DD5.1, выход которого инвертирован, а на входы поступают инвертированные сигналы, исполняет фактически функцию элемента «3MAX», пропуская на выход Y один из входных сигналов X0, X1 или X2.

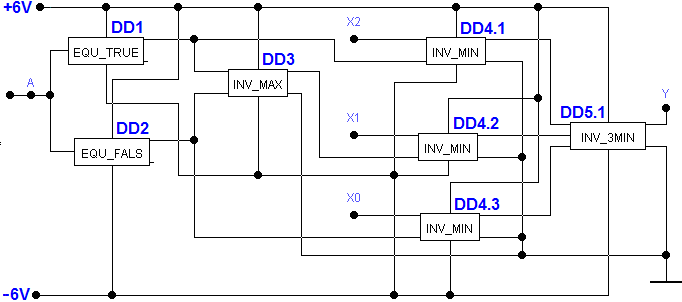

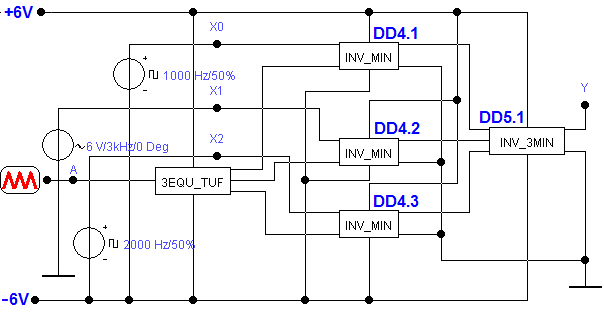

В программе схемотехнического моделирования была разработана модель троичного мультиплексора 3–1, представленная на рисунке ниже.

Элементы DD1, DD2 — декодеры троичных логических уровней «+1» и «–1», соответственно. По совпадению лог. «0» на их выходах элемент DD3, декодирует состояние лог. «0» на входе A уровнем «+1» на своём выходе. При обнаружении соответствующего уровня входе A, элементы DD1, DD2, DD3 открывают активным уровнем «+1» на выходе соответствующие им вентили «INV-MIN» — DD4.1, DD4.2 или DD4.3, в результате чего на выходе Y логического элемента «3INV-MIN» — DD5.1, появляется один из входных сигналов X0, X1 или X2.

Модель была протестирована статическими уровнями на входах, после чего элементы DD1, DD2, DD3 были свернуты в отдельный модуль «3EQU-TUF» для компактности. Модель была исследована в динамике.

На входы X0 и X2 были поданы прямоугольные импульсы амплитудой 12 В с частотами 1000 Гц и 2000 Гц, соответственно. На вход же X1 был подан синусоидальный сигнал амплитудой 6 В и частотой 3000 Гц. На адресный вход мультиплексора A подавался пилообразный сигнал амплитудой 6 В и частотой 200 Гц.

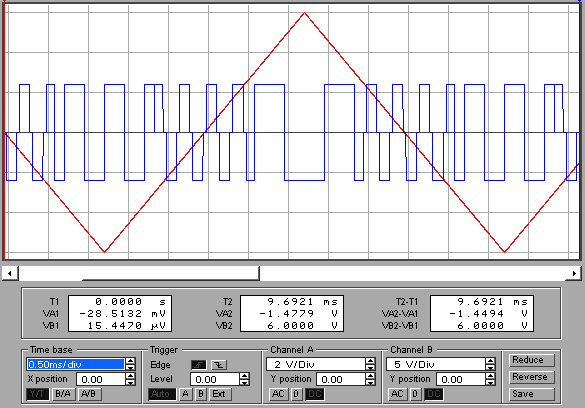

Осциллограммы входного адресного пилообразного сигнала (красный цвет), поданного на вход A устройства, и выходного сигнала (синий цвет) троичного мультиплексора приведены на рисунке ниже.

Осциллограммы демонстрируют, что в диапазоне значений лог. «0» на выходе Y мультиплексора формируется ступенчатый «троичный» сигнал, сформированный вентилем DD4.2 из входной синусоиды частотой 3000 Гц. В диапазоне значений лог. «+1» на выходе мультиплексора наблюдаются прямоугольные импульсы с частотой 1000 Гц, а в диапазоне значений лог. «–1» — с частотой 2000 Гц. Это полностью подтверждает работоспособность модели троичного мультиплексора 3–1.

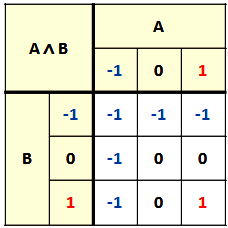

Проанализируем таблицу истинности троичного сумматора по модулю 3 по столбцам в предположении, что его вход A это — вход троичного мультиплексора.

|

|

|

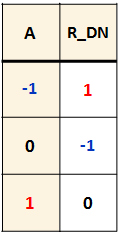

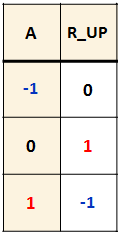

Таблица истинности левой циклической инверсии |

Таблица истинности троичного сумматора по модулю 3 |

Таблица истинности правой циклической инверсии |

Очевидно, что если на входе A уровень лог. «0», то сигналы с входа B проходят на выход троичного сумматора по модулю 3 без изменения, что вполне логично, поскольку сложение любого числа с нулём даст в результате само это число.

Если же на входе A уровень лог. «–1», то сигналы с входа B проходят на выход троичного сумматора по модулю 3 с декрементом на единицу, что соответствует операции левой циклической инверсии (она же — декремент по модулю 3). Это также естественно, поскольку сложение любого числа с «–1» это уменьшение его на единицу.

И, наконец, если на входе A уровень лог. «+1», то сигналы с входа B проходят на выход троичного сумматора по модулю 3 с инкрементом на единицу, что соответствует операции правой циклической инверсии (она же — инкремент по модулю 3). Это также вполне логично, поскольку сложение любого числа с единицей — увеличение его ровно на единицу.

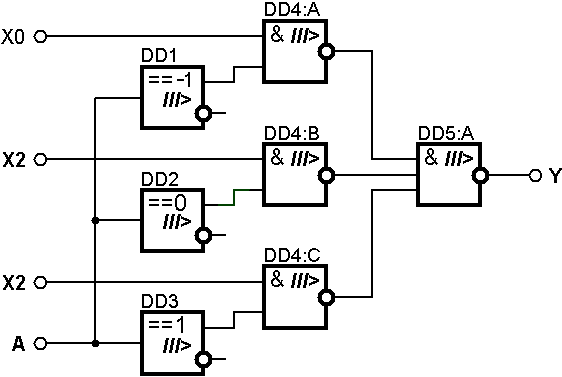

По результатам проведенного выше анализа итоговая схема троичного сумматора по модулю 3 будет выглядеть следующим образом.

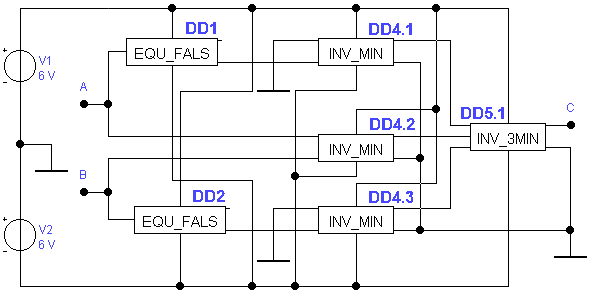

Модель троичного сумматора по модулю 3, разработанная в программе схемотехнического моделирования, представлена на рисунке ниже.

С целью проверки работоспособности устройства на вход A устройства подавался трёхуровневый сигнал (красный цвет), полученный из пилообразного сигнала частотой 1 кГц, пропущенного через троичный вентиль. На вход B устройства последовательно выставлялись логические уровни «–1», «0», «+1».

Ниже представлены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) сумматора по модулю 3 при подаче вход B устройства логического уровня «–1».

Осциллограммы подтверждают, что троичный сумматор по модулю 3 в данном случае вычитает единицу из значений на входе A устройства.

Далее представлены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) сумматора по модулю 3 при подаче вход B устройства логического уровня «0».

Очевидно, что при сложении с нулём на выходе сумматора по модулю 3 формируются те же значения, что и на входе A устройства.

На рисунке ниже приведены осциллограммы сигнала, поданного на вход A устройства (красный цвет), и выходного сигнала (синий цвет) сумматора по модулю 3 при подаче вход B устройства логического уровня «+1».

Из осциллограмм видно, что троичный сумматор по модулю 3 прибавляет единицу к значениям на входе A устройства.

Таким образом, работоспособность сумматор по модулю 3 подтверждена, и для реализации троичного полусумматора необходима схема, отслеживающая факт переноса. Таблица истинности данной схемы представлена ниже.

Очевидно, что необходимость переноса возникает лишь в двух случаях:

- –1 + (–1) = –1 – 1 = +1 — в текущий разряд и –1 — перенос в старший;

- 1 + 1 = –1 – в текущий разряд и +1 — перенос в старший.

Таблица истинности демонстрирует также и другие характерные особенности функции переноса: если один из аргументов равен нулю, нулю равен и результат операции.

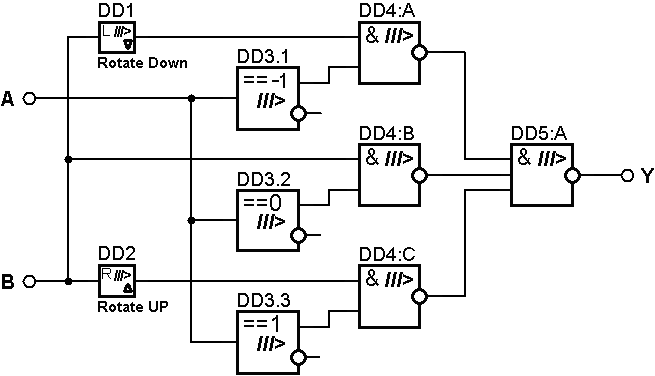

Если в основу схемы заложить трёхвходовый логический элемент «3INV-MAX», как и в предыдущем случае:

И при этом учесть основное свойство элемента «3INV-MAX», заключающееся в том, что он пропускает на выход максимальное из значений на входах, то логику схемы переноса несложно описать следующим образом:

- Если на входе A текущее значение НЕ «–1» — подаём на один из входов элемента «3INV-MAX» «0».

- Если на входе B текущее значение НЕ «–1» — подаём на второй из входов элемента «3INV-MAX» «0».

- Если на входе A и на входе B текущее значение «+1», они подают на два входа элемента «3INV-MAX» «0». Следовательно, необходим элемент, подающий на третий вход элемента «3INV-MAX» «+1», и таким элементом, избирательно реагирующим на совпадение лог. «+1», является «MIN».

- Если на входе A и на входе B текущее значение «–1», подаём на два входа элемента «3INV-MAX» «–1», и элемент «MIN» проделает то же самое.

- В остальных случаях, когда элемент «MIN» выдаёт значение «–1», на входах элемента «3INV-MAX» присутствуют лог.«0», и он выбирает их как максимальные значения.

Для практической реализации рассмотренной выше логики работы схемы переноса в её состав необходимо добавить лишь два декодера логического уровня «–1», и в итоге схема примет следующий вид:

Модель схемы переноса, разработанная в программе схемотехнического моделирования, представлена на рисунке ниже.

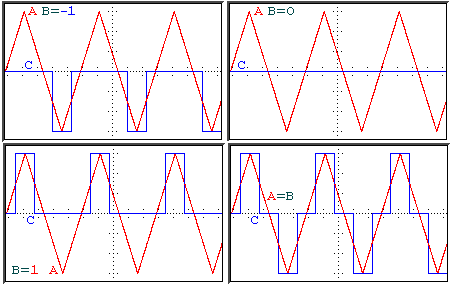

При тестировании устройства на вход B последовательно выставлялись логические уровни «–1», «0», «+1», а вход A устройства подавался пилообразный сигнал (красный цвет) частотой 1 кГц.

Ниже представлены осциллограммы сигнала, поданного на вход A схемы переноса (красный цвет), и выходного сигнала (синий цвет) — трита переноса.

Осциллограммы демонстрируют, что модель схемы переноса функционирует в полном соответствии со своей таблицей истинности, обсуждавшейся выше.

|

|

Сумматор по модулю 3 |

Схема переноса |

Модели сумматора по модулю 3 и схемы переноса была оформлены в виде отдельных функциональных модулей «SUM_MOD3» и «T_CARRY» (Trit CARRY — трит переноса) соответственно, которые в дальнейшем были использованы для построения троичного полного одноразрядного сумматора, что, впрочем, не ограничивает их применение и в составе прочих устройств троичной логики.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download