Модели КМОП транзисторов в программе

Electronics Workbench

В настоящее время в цифровой технике наиболее широко распространены две технологии логических элементов: ТТЛ и КМОП. ТТЛ — Транзисторно–Транзисторная Логика; КМОП — Комплементарные полевые транзисторы со структурой Металл – Окисел – Полупроводник (MOSFET — Metal–Oxide–Semiconductor Field–Effect Transistor).

Термин «комплементарный» в данном случае означает «взаимно дополняющий». Пара полевых транзисторов является комплементарной, если они обладают каналами противоположного типа проводимости, а по остальным параметрам идентичны.

Элементы, выполненные по КМОП–технологии, являются на сегодняшний день доминирующими при производстве цифровых интегральных схем и в значительной мере потеснили логику на основе биполярных транзисторов. Это обусловлено следующими причинами.

- Логические элементы, изготовленные по КМОП–технологии, потребляют значительно меньшую мощность, чем логические элементы на основе биполярных транзисторов, как в статическом, так и в динамическом режимах. Потребление мощности КМОП–элементами обусловлено в основном перезарядом паразитных емкостей при переключении элемента из одного логического состояния в другое.

- Поскольку входы схем являются изолированными затворами МОП–транзисторов, то входные токи очень малы. Поэтому коэффициент разветвления по выходу очень высок. Высокое входное сопротивление МОП–транзисторов позволяет использовать накопленный заряд для хранения входной информации. Это свойство широко используется в микросхемах памяти.

- МОП–транзистор занимает на кристалле значительно меньшую площадь, чем биполярный. Современные технологии производства СБИС позволяют создавать МОП–транзисторы с длиной канала 0.06 мкм. Уменьшение геометрических размеров, а также малое потребление мощности дают возможность изготавливать СБИС, которые содержат десятки миллионов МОП–транзисторов.

- Сравнительная простота МОП–технологии: для реализации простейшей работоспособной n-МОП или p-МОП схемы нужны всего четыре фотолитографии, для КМОП — шесть, а для биполярной схемы литографий нужно семь для одного типа транзисторов, и еще необходим более точный контроль диффузий и, в идеале, эпитаксия.

В семействе полевых МОП–транзисторов выделяют 4 основных вида, представленных в следующей таблице:

N–канальный полевой транзистор с изолированным затвором и встроенным каналом (N–Channel Depletion Mode MOSFET) обеднённого типа — нормально открытый.

P–канальный полевой транзистор с изолированным затвором и встроенным каналом (P–Channel Depletion Mode MOSFET) обеднённого типа — нормально открытый.

N–канальный полевой транзистор с изолированным затвором и индуцированным каналом (N–Channel Enhancement Mode MOSFET) обогащённого типа — нормально закрытый.

P–канальный полевой транзистор с изолированным затвором и индуцированным каналом (P–Channel Enhancement Mode MOSFET) обогащённого типа — нормально закрытый.

Как видно из приведённых в таблице вольтамперных характеристик, нормально закрытые транзисторы с индуцированным каналом не проводят ток при нулевом напряжении затвор–исток. В то время как нормально открытые транзисторы со встроенным каналом проводят ток при тех же условиях, и для того, чтобы их закрыть, между затвором и истоком следует приложить запирающий потенциал, равный или превышающий значение напряжения отсечки.

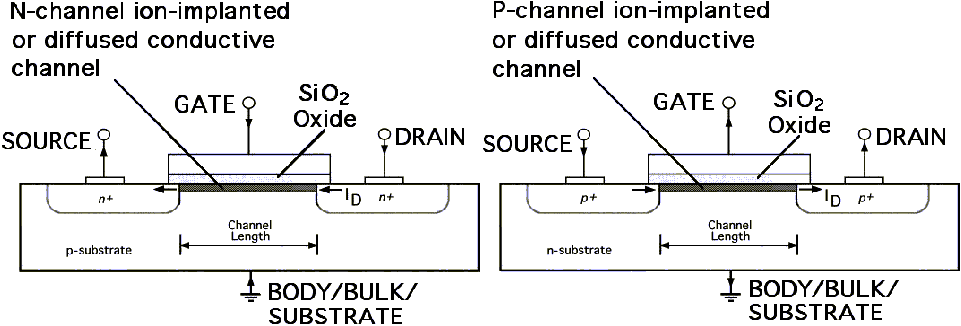

Технологически полевые транзисторы со встроенным каналом отличаются от приборов с индуцированным каналом тем, что в подзатворной области методом диффузии или ионной имплантации формируется тонкий проводящий слой.

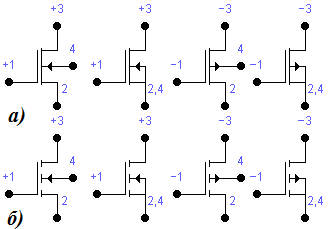

В библиотеке компонентов системы схемотехнического моделирования и анализа электронных схем [Карлащук В.И. Электронная лаборатория на IBM PC. Программа Electronics Workbench и ее применение. Изд. 3-е, переработанное и дополненное. - М.: СОЛОН-Пресс, 2008. - 736 с.: ил.] комплементарные МОП–транзисторы со встроенным (а) и индуцированным (б) каналом представлены следующими образцами:

Каждый тип МОП–транзистора представлен в двух вариантах: с отдельным выводом подложки и общим выводом подложки и истока. На рисунке цифрами обозначены: 1 — затвор (Gate), 2 — исток (Source), 3 — сток (Drain), 4 — подложка (Bulk).

Эквивалентные схемы МОП–транзисторов в системе схемотехнического моделирования соответствуют простой модели первого уровня (Level 1) программы PSpice [Разевиг В.Д. Применение программ P-CAD и PSpice для схемотехнического моделирования на ПЭВМ: В 4 выпусках. Вып. 2: Модели компонентов аналоговых устройств. — М.: Радио и связь, 1992. — с.24]

Структура МОП–транзистора с каналом n–типа, представленная на рисунке ниже:

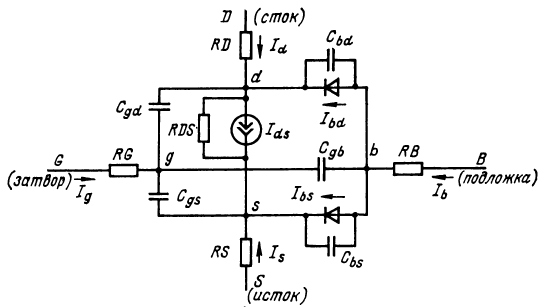

Представляется следующей нелинейной схемой замещения:

Ниже — пример PSpice модели МОП–транзистора первого уровня, представленного приведенной выше схемой замещения:

.MODEL ideal NMOS (

+ VTO = 0

+ KP = 2e-05

+ LAMBDA = 0

+ PHI = 0.6

+ GAMMA = 0

+ RD = 0

+ RS = 0

+ IS = 1e-14

+ CGBO = 0

+ CGDO = 0

+ CGSO = 0

+ CBD = 0

+ CBS = 0

+ PB = 0.8

+ RSH = 0

+ CJ = 0

+ MJ = 0.5

+ CJSW = 0

+ MJSW = 0.5

+ JS = 0

+ TOX = 1e-07

+ NSUB = 0

+ NSS = 0

+ TPG = 1

+ LD = 0

+ U0 = 600

+ KF = 0

+ AF = 1

+ FC = 0.5

+ TNOM = 27

)

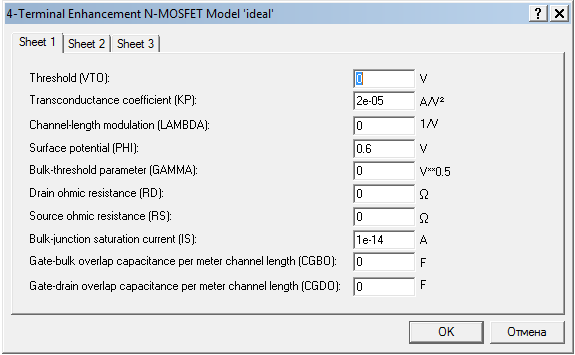

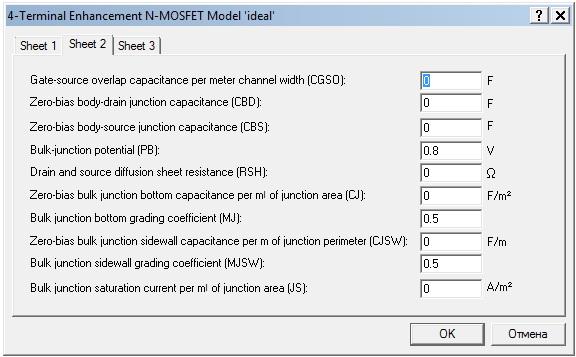

Параметры PSpice модели МОП–транзистора подробно обсуждаются в упомянутой выше литературе, а в системе схемотехнического моделирования и анализа электронных схем их редактирование возможно на следующих вкладках:

Комплементарные МОП–транзисторы с изолированным затвором позволяют создать как логический инвертор, так и другие логические элементы, практически не потребляющие энергию источника питания как в состоянии логического «нуля» на входе, так и в состоянии логической «единицы». Схемотехника их будет обсуждаться далее.