Троичные D-триггер и счетный триггер

В двоичной цифровой технике D–триггером называют синхронный триггер, имеющий два входа — вход данных D и вход синхронизации С.

Схемотехнически D–триггер устраняет запрещенное состояние синхронного RS–триггера, подачей сигнала данных с входа D на входы R и S в противофазе.

Варианты схемотехнического исполнения D–триггера в традиционной цифровой технике приведены на рисунках ниже.

|

|

D–триггер — элементарная ячейка хранения данных (от англ. Data) в синхронных цифровых системах, или триггер задержки (от англ. delay – задержка), при разрешающем сигнале на тактовом входе C устанавливает на прямом выходе Q состояние, соответствующее логическому сигналу на входе D.

D–триггер, действительно, осуществляет задержку появления на выходе Q состояния входа D на интервал времени до подачи разрешающего сигнала на тактовом входе C.

D–триггер, выполненный по одной из приведенных выше схем, называют D–триггером с управлением уровнем или же статическим синхронным D–триггером, изменение состояния выходов которого происходит только в те моменты времени, когда на его синхронизирующий вход поступает тактирующий импульс.

Поскольку на время действия тактирующего импульса выходы D–триггера повторяют изменение состояния на входе D, триггер такого типа называют также «прозрачной защелкой». Следствием этого является тот факт, что D–триггер прозрачного типа критичен к длительности тактирующего импульса на входе C.

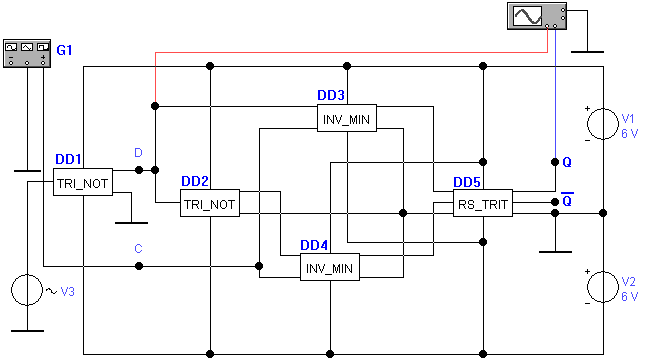

На основе троичных логических элементов «INV-MIN» и троичного инвертора в программе схемотехнического моделирования была реализована модель троичного синхронного D–триггера, схема которого приведена на следующем рисунке.

С её помощью была измерена таблица логических переходов устройства, представленная ниже.

Из представленных в таблице данных очевидно, что при поступлении на вход синхронизации логической «1» (высокий уровень напряжения), троичный D–триггер включается в режим записи (становится прозрачным для входных сигналов), считывая информацию, поступающую на вход D, и передавая её на выходы. Возможна запись одного из трёх логических состояний: «+1», «0» и «–1».

При подаче на вход синхронизации логической «–1» (низкий уровень напряжения) и перехода «+1» → «–1» на входе C, триггер хранит записанную информацию.

При включении синхронный троичный D–триггер устанавливается в устойчивое логическое состояние Q = «0», /Q = «0».

Подача на вход синхронизации логического «0» противоречит логике работы троичного D–триггера, и такой режим считается нештатным.

В неустоявшейся окончательно терминологии троичной логики это устройство называют «D–триттер», чтобы отличать от его двоичного аналога.

Модель D–триттер была протестирована в динамике, как это показано на схеме ниже.

На вход D троичного триггера подавался трёхуровневый сигнал, сформированный инвертором DD1 из синусоидального сигнала источника V3 частотой 500 Гц и амплитудой 6 В.

На вход C подавался импульсный синхросигнал от источника G1 частотой 3 кГц, амплитудой 12 В и скважностью 50. Частоты синхросигнала и сигнала данных были выбраны в соотношении 6 : 1, чтобы синхроимпульс приходился на все части трёхуровневого сигнала.

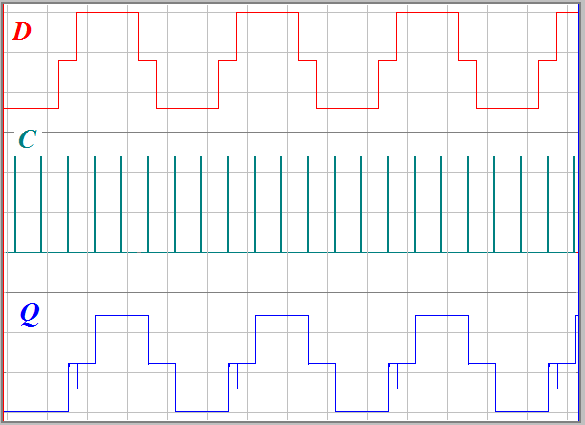

Ниже показаны осциллограммы сигналов во время тестирования D–триттера в динамике.

Очевидно, что D–триттер успешно фиксирует на своём выходе Q трёхуровневый входной сигнал по стробирующему импульсу на входе C с задержкой на период синхросигнала.

Следует обратить внимание на тот факт, что аналоговые модели троичных логических элементов позволяют наблюдать все особенности переходных процессов при переключении, как это отчетливо видно на осциллограмме сигнала с выхода Q триттера (синий цвет).

Поскольку модель D–триттера демонстрирует успешную и бессбойную работу, представляет интерес протестировать её в режиме счетного триттера (T–триттера).

В двоичной цифровой технике Т–триггер фактически выполняет операцию сложения по входным импульсам, что, собственно, и обусловило название такого триггера счетным, а его информационный (Т) вход – счетным входом. Счётный триггер изменяет состояние своих выходов на противоположное при каждом перепаде тактового импульса.

Технически такой двоичный триггер может быть реализован на основе двоичного же D–триггера, если соединить его информационный вход D с инверсным выходом /Q, как это показано на рисунке ниже.

В троичной технике ситуация более сложная. Если выполнить троичный счетный триггер так, как это показано на рисунке выше, он не сможет считать принципиально по той причине, что в троичной логике инверсия логического «0» есть сам логический «0». И в этом случае логический «0» с инверсного выхода /Q будет переписываться на прямой выход Q по тактовым импульсам, что практически означает отсутствие счета как такового.

Следовательно, для создания троичного счетного триггера D–триттер необходимо дополнить по выходу элементом левой или правой циклической инверсии, поскольку именно эти элементы выполняют в троичной логике функции декремента и инкремента по модулю 3.

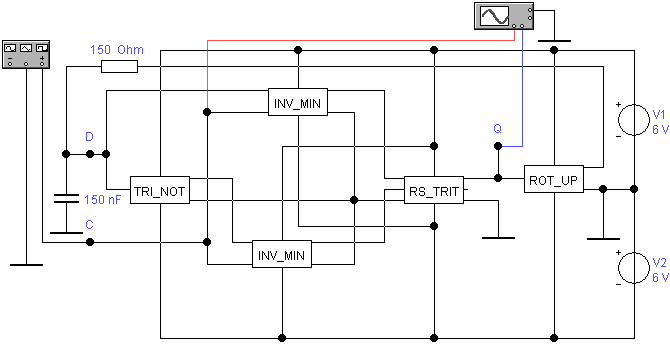

Модель троичного счетного триггера была реализована в программе схемотехнического моделирования на основе D–триттера и элемента правой циклической инверсии по схеме, приведенной на следующем рисунке.

Поскольку D–триттер является прозрачным триггером–защелкой, довольно непросто подобрать длительность стробирующего импульса такой, чтобы с одной стороны D–триттер успел переписать значение с выхода элемента правой циклической инверсии, с другой стороны этот импульс должен быть достаточно коротким, чтобы не возник процесс генерации на длительности задержки распространения импульса в цепи D–триттера.

Для устранения этого эффекта в контур обратной связи был введён элемент задержки в виде RC–цепи.

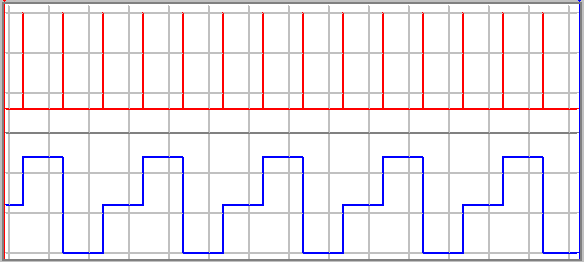

Ниже представлены осциллограммы счёта на увеличение троичного Т–триггера, выполненного на основе D–триттера.

Тактирование осуществлялось импульсным сигналом частотой 10 кГц, амплитудой 12 В и скважностью 100.

Модель троичного счетного триггера, осуществляющего счет на уменьшение, реализованная в программе схемотехнического моделирования на основе D–триттера и элемента левой циклической инверсии, представлена на следующем рисунке.

Для устранения нежелательной высокочастотной генерации в контур обратной связи был также введён элемент задержки в виде RC–цепи.

Тактирование модели осуществлялось также импульсным сигналом частотой 10 кГц, амплитудой 12 В и скважностью 100.

Ниже представлены осциллограммы счёта на уменьшение троичного Т–триггера, выполненного на основе D–триттера и элемента левой циклической инверсии.

Следует подчеркнуть, что применение одноступенчатых статических синхронных триггеров в качестве самостоятельных узлов счетных схем весьма и весьма ограничено фактом их «прозрачности», что приводит к неустойчивой работе последовательностных схем (цифровых автоматов), выполненных на их основе.

Тем не менее, они являются основой для более сложных устройств — двухступенчатых триггеров или MS-триггеров, устройство которых в троичной цифровой технике будет рассмотрено далее.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download