Логические элементы – декодеры троичных логических уровней

Декодер в общем случае — некоторое звено, узел в каком-либо устройстве, в задачу которого входит преобразование информации из одного внешнего вида в другой вид.

В том аспекте, в котором сейчас пойдёт речь о декодерах, они представляют собой унарные функции одного аргумента, преобразующие трёхзначный код на входе в строго двухзначный код на выходе [Standard Ternary Logic by Douglas W. Jones].

Функции имеют следующий вид:

F(a) = (a = –1) — обнаружено логическое состояние «ЛОЖНО»;

F(a) = (a = 0) — обнаружено логическое состояние «НЕИЗВЕСТНО»;

F(a) = (a = +1) — обнаружено логическое состояние «ИСТИННО».

Входной код может принимать все три значения: «ИСТИННО», «ЛОЖНО» и «НЕИЗВЕСТНО», тогда как код на выходе может принимать лишь два значения: «ИСТИННО» и «ЛОЖНО». В этом плане устройства, действительно, являются декодерами, хотя не будет ошибкой назвать их детекторами троичных логических сигналов «–1», «0», «+1». Обнаружив на входе логический сигнал соответствующего уровня, детектор выдаёт на выход сигнал «+1», во всех остальных случаях — «–1», сигнал «0», «НЕИЗВЕСТНО» не может появиться на выходе никогда.

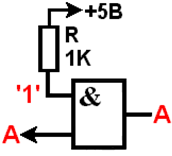

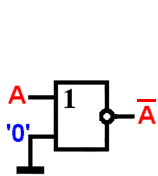

Если для понимания сути работы этих декодеров необходима аналогия в двоичной цифровой технике, то, пожалуй, наиболее понятно иллюстрируют суть следующие схемы:

|

|

Двоичный декодер лог. «1» |

Двоичный декодер лог. «0» |

Логический элемент «И» избирательно реагирует на совпадение лог. «1» на входах, следовательно, в этом случае на выходе будет лог. «1».

Логический элемент «ИЛИ–НЕ», избирательно реагирует на совпадение лог. «0» на входах, следовательно, в этом случае на выходе будет лог. «1», поскольку на выходе инверсия.

Пример сугубо абстрактный, поскольку, строго говоря, представленные на рисунках устройства декодерами не являются, так как сигналы на входе и на выходе в обычной двоичной кодировке.

Возможно, более корректно на роль такого декодера в двоичной цифровой технике может претендовать триггер Шмитта.

Триггер Шмитта относится к несимметричным триггерам и предназначен для формирования из входного непрерывно меняющегося сигнала выходного импульсного, имеющего два уровня: уровень лог. «0» и уровень лог. «1».

Следует помнить, что реальные логические устройства не являются идеальным воплощением Булевых функций, которые они реализуют. Им присущи задержки распространения, они фактически представляют собой аналоговые усилители с довольно высоким коэффициентом усиления, поэтому в реальных условиях на работу цифровых устройств негативно влияют реактивности как паразитные, так и являющиеся составной частью самих устройств. Из-за этого возможны ситуации, которые не отражают формулы алгебры логики: возникают «гонки», «иголки», на пологих фронтах возможно возникновение, как генерации, так и хаотических пакетов импульсов под влиянием помех. Но для того чтобы минимизировать влияние все этих негативных факторов в схемотехнике двоичных цифровых устройств существует набор известных схемотехнических решений, которые освещаются в специальной литературе, в частности, хорошим источником может служить [Потемкин И.С. Функциональные узлы цифровой автоматики, М.: Энергоатомиздат. 1988. 320 с.]. Применение триггера Шмитта является лишь частным случаем подобных схемотехнических решений.

Известно, что сложные двоичные цифровые системы, к числу которых относится и процессор, строятся по синхронному принципу — в основе системы есть задающий генератор, определяющий минимальное время системы – такт, есть также счётчики тактов, позволяющие осуществлять «привязку» отдельных событий в системе к конкретным тактам.

Сложные троичные цифровые системы также строятся по синхронному принципу, но поскольку троичный сигнал трёхуровневый, с декодированием отдельных тактов возникают определённые сложности.

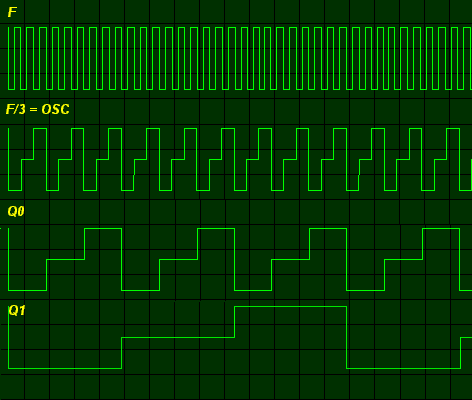

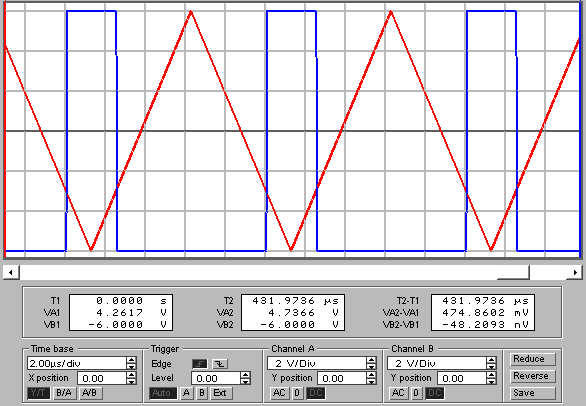

Рассмотрим осциллограмму работы троичного счётчика, приведенную на рисунке ниже.

Отдельные события в троичной цифровой системе могут происходить в привязке к логическим уровням «1», «0» и «–1». Обратим теперь внимание на таблицы истинности «строительных кирпичиков» троичных систем — логических элементов:

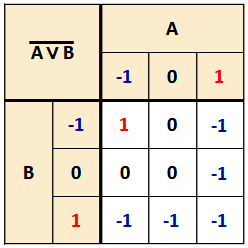

|

|

| INV-MIN | INV-MAX |

Очевидно, что троичные логические элементы «INV-MIN» (аналог двоичного «И–НЕ») и «INV-MAX» (аналог двоичного «ИЛИ–НЕ») обладают свойствами своих двоичных аналогов: логический элемент «INV-MIN» избирательно реагирует на совпадение лог.«1» на входах, а логический элемент «INV-MAX» избирательно реагирует на совпадение лог. «–1» на входах. Но из таблиц также видно, что оба этих троичных логических элемента реагируют и на уровень лог. «0»!

В этой связи возникают естественные вопросы: как же декодировать троичные уровни счётчика на основе таких логических элементов? И как избегать помех и случайных сбоев в следующих ситуациях?

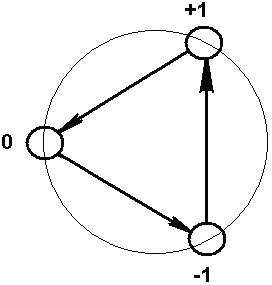

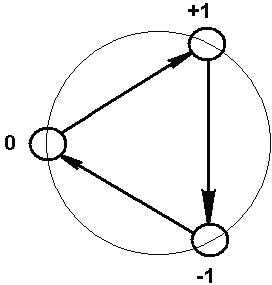

|

|

Как видно из приведенных выше диаграмм, в троичной цифровой системе переходы между уровнями «–1» → «+1» и «+1» → «–1» фактически всегда проходят через уровень лог.«0». Как это будет отражаться на помехоустойчивости системы? Не будет ли это вызывать непредусмотренного срабатывания троичных логических схем?

Декодеры троичных логических уровней «–1», «0», «+1» как раз и призваны корректно разрешить эти проблемы, а также упростит построение дешифраторов троичного сигнала, и обеспечить надёжное согласование с двоичными логическими элементами, а также многое другое.

Подчеркнём основное свойство этих логических элементов: обнаружив на входе логический сигнал соответствующего уровня, декодер выдаёт на выход сигнал «+1», во всех остальных случаях — «–1», сигнал «0», «НЕИЗВЕСТНО» не может появиться на выходе никогда.

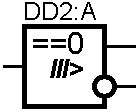

Поскольку условные графические обозначения для таких элементов не были предусмотрены, предложено изображать их следующим образом:

|

|

|

Декодер троичного уровня лог. «–1» |

Декодер троичного уровня лог. «0» |

Декодер троичного уровня лог. «+1» |

Поскольку при построении дешифраторов удобно иметь как сам сигнал, так и его инверсию, у декодеров выведены и инверсные значения сигнала, поскольку схемотехнически это проще, нежели подключать отдельно внешний инвертор.

Троичные логические элементы обозначены на схеме знаком «III>», что соответствует ГОСТ 2.743-91 ЕСКД Обозначения условные графические в схемах. Элементы цифровой техники — римская цифра «III» со стороны входов свидетельствует о том, что элементы работают с входными сигналами троичной логики, а стилизованная стрелка «>», указывающая на выходы элемента, подчёркивает тот факт, что выходные сигналы также троичные.

Рассмотрим схемотехнику троичных логических декодеров подробно.

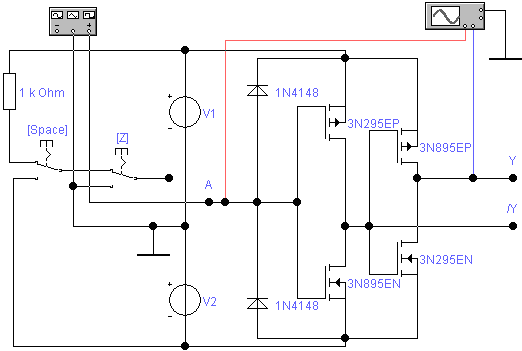

Ниже представлена электрическая принципиальная схема декодера логического уровня «–1».

Схема декодера очень проста. Компаратор логического уровня «–1» выполнен на МОП–транзисторах VT1 и VT2. Их пороговые напряжения выбраны так, что когда входной сигнал достигает потенциала лог. «–1», транзистор VT2 закрывается, а транзистор VT1 открывается, соединяя выход схемы Y с шиной положительного потенциала источника V1, тем самым формируя на выходе Y уровень лог. «1».

МОП–транзисторы VT3 и VT4 образуют инвертор сигнала с выхода Y и выдают на выход /Y сигнал в противофазе. (Здесь и далее символ « / » обозначает инверсию соответствующего сигнала.)

Диоды VD1 и VD2 выполняют защитную функцию, а также вносят во входной импеданс устройства свою емкостную составляющую при моделировании схемы.

На рисунке ниже представлена модель троичного декодера логического уровня «–1», выполненная в программе схемотехнического моделирования. Во входных цепях предусмотрена возможность коммутировать логические сигналы вручную с помощью двух переключателей, управляемых клавишами [Space] и [Z]. Резистор номиналом 1 кОм формирует сигнал лог. «1», переключатели позволяют подать на вход A потенциалы лог. «0» и лог. «–1».

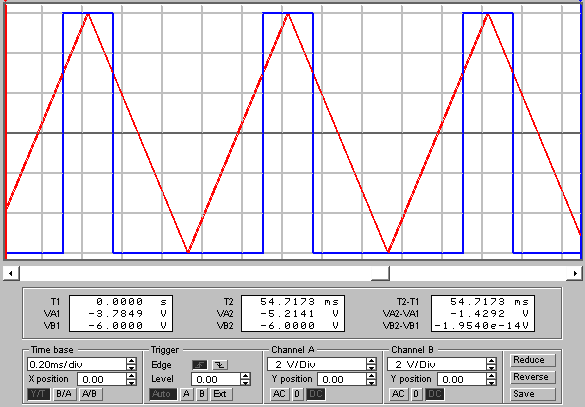

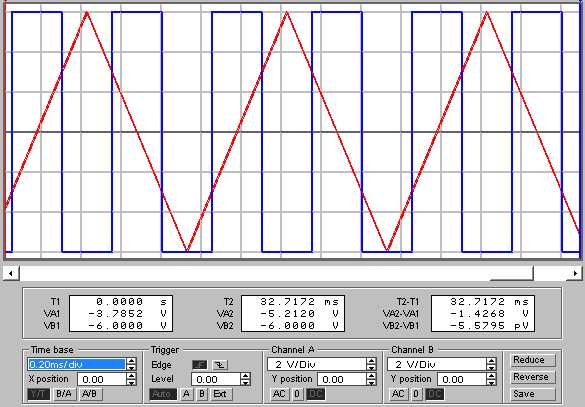

Ниже приведены осциллограммы входного пилообразного сигнала (красный цвет), поданного на вход A устройства, и выходного сигнала (синий цвет) троичного декодера логического уровня «–1», на частоте входного пилообразного сигнала — 1 кГц.

Очевидно, что выходной сигнал Y (синий цвет) принимает значение лог. «1» всякий раз, когда входной пилообразный сигнал (красный цвет) достигает потенциала, соответствующего уровню лог. «–1».

Модель была оформлена в виде отдельного функционального модуля «EQU_FALS» (EQUivalent to FALSe – эквивалентно уровню «ЛОЖЬ»), который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Представленный на рисунке выше функциональный модуль «EQU_FALS», соответствует условному графическому обозначению троичного декодера логического уровня «–1».

Принципиальная электрическая схема декодера троичного логического уровня «+1» представлена на следующем рисунке.

Компаратор логического уровня «1» также выполнен на МОП–транзисторах VT1 и VT2. Но в этом случае их пороговые напряжения выбраны так, что когда входной сигнал достигает потенциала лог. «1», транзистор VT1 закрывается, а транзистор VT2 открывается, соединяя выход схемы /Y с шиной отрицательного потенциала источника V2, тем самым формируя на выходе Y уровень лог. «–1».

МОП–транзисторы VT3 и VT4 образуют инвертор сигнала с выхода /Y и выдают на выход Y сигнал в противофазе.

Диоды VD1 и VD2 выполняют защитную функцию, а также вносят во входной импеданс устройства свою емкостную составляющую при моделировании схемы.

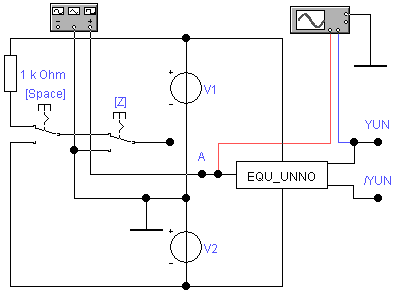

На рисунке ниже представлена модель троичного декодера логического уровня «–1», выполненная в программе схемотехнического моделирования.

Во входных цепях предусмотрена возможность коммутировать при необходимости логические сигналы вручную с помощью двух переключателей, управляемых клавишами [Space] и [Z]. Резистор номиналом 1 кОм формирует сигнал лог. «1», переключатели позволяют подать на вход A потенциалы лог. «0» и лог. «–1».

На следующем рисунке приведены осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A троичного декодера логического уровня «+1», и его выходного сигнала (синий цвет).

На осциллограммах видно, что сигнал на выходе Y (синий цвет) принимает значение лог. «1» всякий раз, когда входной пилообразный сигнал (красный цвет) достигает потенциала, соответствующего уровню лог. «1».

Модель была оформлена в виде отдельного функционального модуля «EQU_TRUE» (EQUivalent to TRUE – эквивалентно уровню «ИСТИНА»), который может быть использован в дальнейшем для построения более сложных устройств троичной логики.

Представленному на рисунке выше функциональному модулю «EQU_TRUE», соответствует условное графическое обозначение троичного декодера логического уровня «1».

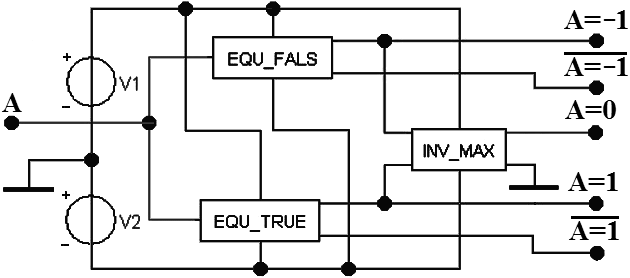

Практика разработки схем троичной логики показала, что в декодере логического уровня «0» возникает необходимость сравнительно нечасто. Но в тех случаях, когда он, действительно, необходим, в схеме уже присутствуют чаще всего декодеры логических уровней «–1», «+1».

Поэтому декодер логического уровня «0» был выполнен по следующей схеме, представленной на рисунке ниже.

Выходные сигналы двух разработанных ранее функциональных модулей декодеров «EQU_FALS» и «EQU_TRUE» контролирует троичный логический элемент «INV MAX», избирательно реагирующий на совпадение лог. «–1» на своих входах. Следовательно, когда декодеры «EQU_FALS» и «EQU_TRUE» не обнаружили ни лог. «–1», ни лог. «1», на их выходах присутствуют сигналы лог. «–1», на совпадение которых и реагирует логический элемент «INV MAX», выставляя на своём выходе сигнал лог. «1», свидетельствующий о том, что на входе устройства присутствует уровень лог. «1».

Схема в таком виде удобна ещё и тем, что на её выходах присутствуют одновременно сигналы контроля всех трёх троичных логических уровней, что в значительной мере упрощает построение дешифраторов.

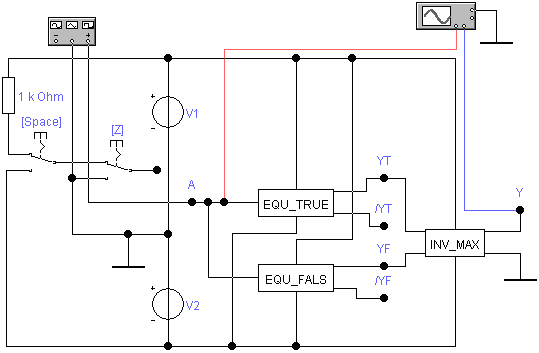

По приведенной выше схеме в программе схемотехнического моделирования была разработана модель троичного декодера логического уровня «0». Модель представлена на рисунке ниже.

Ниже осциллограммы входного пилообразного сигнала (красный цвет) частотой 1 кГц, поданного на вход A троичного декодера логического уровня «0», и сигнала на выходе Y (синий цвет).

Очевидно, что выходной сигнал Y (синий цвет) принимает значение лог. «1» всякий раз, когда входной пилообразный сигнал (красный цвет) проходит через область потенциалов, соответствующую уровню лог. «0».

Как уже было сказано выше, представленная схема троичного декодера логического уровня «0» удобна тем, что на её выходах присутствуют одновременно сигналы контроля всех трёх троичных логических уровней, что в значительной мере упрощает построение дешифраторов.

Поскольку программа схемотехнического моделирования ориентирована на разработку и тестирование узлов и устройств двоичной логики, в ней отсутствуют удобные средства статической индикации для троичных логических уровней. Пользоваться осциллографом в ряде случаев весьма неудобно, поэтому первым функциональным модулем, включающим в свой состав схему троичного декодера логического уровня «0» в том виде, как она представлена выше, был полный дешифратор троичного сигнала в двоичные логические уровни. Это позволило подключить к нему цветные элементы двоичной статической индикации, и использовать при отладке устройств троичной логики.

Модель дешифратора представлена на следующем рисунке.

На выход дешифратора выведены выходные сигналы всех трёх декодеров троичных логических уровней — лог. «–1», лог. «0», и лог. «1». Они управляют статическими двоичными индикаторами двоичных логических уровней синего, зелёного и красного цветов соответственно. Индикатор на основе дешифратора оказался весьма удобным инструментом при отладке троичных логических схем.

При создании функционального модуля троичного декодера логического уровня «0», получившего соответствующее название «EQU_UNNO» (EQUivalent to UNkNOwn – эквивалентно уровню «НЕИЗВЕСТНО»), схема была оптимизирована: из неё были исключены избыточные компоненты. Довольно странное сокращение обусловлено тем, что название модуля ограничено восьмью символами, а сокращение «EQU_UNKN» более непонятно на вид.

Представленному на рисунке выше функциональному модулю «EQU_UNNO», соответствует следующее условное графическое обозначение троичного декодера логического уровня «0».

В завершение обсуждения принципов работы и схем троичных декодеров логических уровней необходимо напомнить, что разработанные троичные логические элементы INV–MIN», «INV–MAX» и троичный инвертор не образуют функционально полный логический базис, на основе которого можно реализовать любое, сколь угодно сложное троичное комбинационное устройство.

Для полноты базису недостаёт специфического устройства, также не имеющего аналога в двоичной логике, способного осуществлять преобразование лог. «–1» в лог. «0», лог. «0» в лог. «1» и лог. «1» в лог. «–1» или же в обратном порядке: лог. «–1» в лог. «1», лог. «1» в лог. «0» и лог. «0» в лог. «–1». Подобное преобразование в троичной логике носит название «циклическая инверсия». И декодеры троичных логических уровней окажутся востребованы в схемотехнике логических элементов троичных циклических инверсий.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download