Троичный дешифратор и шифратор

Дешифратор (decoder) — комбинационное устройство, позволяющее распознавать числа, представленные позиционным n–разрядным кодом.

Дешифратор типа «код–позиция» преобразует входной n–разрядный двоичный код в унитарный (позиционный) код.

В двоичной технике, если на входе дешифратора n–разрядный двоичный код, то на его выходе — код «1 из N». В кодовой комбинации этого кода только одна позиция активна единичным или нулевым уровнем, а все остальные — неактивны.

Синтез дешифратора осуществляется по принципам аналогичным для любого двоичного цифрового устройства, для которого записана таблица истинности.

Запись логической функции по таблице истинности производится в виде совершенной дизъюнктивной нормальной формы (СДНФ) или совершенной конъюнктивной нормальной формы (СКНФ). Для составления логической формулы в СДНФ выбирают в таблице истинности строки, где логическая функция y = 1. Если число таких строк обозначить как Р, то далее записывают логическую сумму Р произведений всех переменных xi, причем в произведении xi, соответствующем данной отдельной строке, записывают без инверсии, если хi = 1 и с инверсией, если xi = 0. Такие произведения называют минтермами.

Синтез дешифратора типа «код–позиция» упрощается тем, что на его выходе — код «1 из N», следовательно, для каждой строки достаточно записать произведение всех переменных xi, а логическую сумму Р произведений записывать нет необходимости в силу специфики выходного кода, когда каждой строке соответствует уникальное состояние одного из выходов.

Рассмотрим в качестве примера синтез дешифратора типа «код–позиция» на три входа. Поскольку дешифрация будем производиться из двоичного позиционного кода по степеням числа 2 — «8–4–2–1» — обозначим входы как a1, a2, a4. Поскольку дешифратор полный, то есть, для каждой из всех возможных входных комбинаций существует единственный выход со своим уникальным состоянием, число таких выходов будет равно 23 или 8.

Запишем таблицу истинности с учетом того, что активным состоянием отдельного выхода Qi (i = 0…7) является уровень логической «1».

Таблица истинности дешифратора на три входа с активным единичным уровнем входных и выходных сигналов представлена ниже.

В соответствии с принципом синтеза логических схем по заданной таблице истинности необходимо для каждого выхода написать логическое выражение. В данном случае, как уже было сказано ранее, задача упрощается, поскольку для каждого выхода логическая 1 имеет место быть только в одной строке таблицы. Поэтому в логическом выражении для каждого выхода будет только один минтерм:

Ниже показана функциональная схема дешифратора, соответствующая логическим выражениям, приведенным выше.

Переходя к реалиям троичной логики, можно согласиться с определением: дешифратор (decoder) — комбинационное устройство, позволяющее распознавать числа, представленные позиционным n–разрядным кодом, поскольку тип кода в общем случае явно не указан.

Троичный же дешифратор типа «код–позиция» преобразует входной n–разрядный троичный код в унитарный (позиционный) код, причем код этот будет явно совместим с узлами двоичной логики.

В силу этого принципы построения троичного дешифратора типа «код–позиция» существенных отличий от принципов реализации двоичного дешифратора не имеют, за исключением того, что каждый разряд троичного кода предварительно декодируется фактически в три бита по соответствию его троичным логическим уровням «–1», «0», «+1».

Декодированные значения можно обработать двоичными логическими элементами согласно правилам синтеза устройства по заданной таблице истинности, причем задача упрощается, поскольку для каждого трита после его декодирования лог. «+1» может быть только одним из трёх значений.

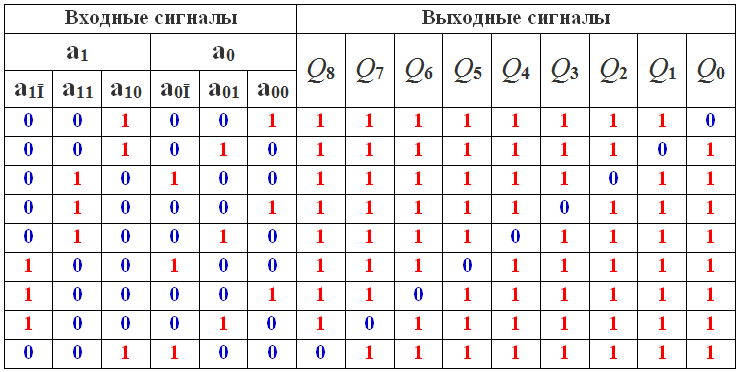

Рассмотрим в качестве примера синтез троичного дешифратора типа «код–позиция» на два входа. Дешифратор полный, следовательно, для каждой из всех возможных входных троичных комбинаций существует единственный выход со своим уникальным состоянием, число таких выходов будет равно 32 или 9. Отметим это преимущество троичной позиционной системы: в двух её разрядах содержится больший объём информации, нежели в трёх разрядах двоичной системы.

Для удобства составления таблицы истинности приведем диаграмму работы троичного двухразрядного асинхронного счётчика, на которой обозначены числа, соответствующие работе декодера.

Отметим, что отрицательные числа означают заём из старшего разряда, который в троичной симметричной позиционной системе равен в данном случае 32 или 9.

Очевидно, что из-за особенностей декодирования разрядов троичной симметричной позиционной системы в каждой строке входных значений встречаются лишь по две значащих лог. «1». В принципе для построения необходимых произведений для каждой строки было бы достаточно двоичных логических элементов «И-НЕ», поскольку логическая операция «И» избирательно реагирует на совпадение лог. «1».

Для удобства применения дешифратора в схеме были задействованы элементы «3И-НЕ», для организации входа управления «разрешение по выходу» (/OE — Output Enable).

Принципиальная электрическая схема троичного дешифратора типа «код–позиция» на два входа, представлена на рисунке ниже.

Элементы DD1, DD2, DD3 — декодеры троичных логических уровней «0», «+1», «–1», соответственно, входного сигнала a0. Элементы DD4, DD5, DD6 — декодеры троичных логических уровней «0», «+1», «–1», соответственно, входного сигнала a1. Элемент DD7 — декодер троичного логического уровня «–1», детектирующий сигнал «разрешение по выходу» (/OE — Output Enable) низкого уровня и выдающий сигнал «+1» на входы элементов «3И-НЕ» DD8…DD10, разрешающий их одновременную работу по совпадению лог. «+1» на входах.

Элементы «3И-НЕ» DD8…DD10 каждый по двум оставшимся входам контролируют совпадение сигналов «+1» с выходов декодеров троичных логических уровней согласно таблице истинности, приведенной ранее.

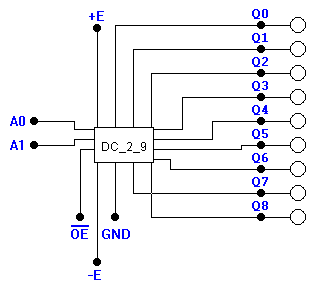

Схема троичного дешифратора типа «код–позиция» на два входа была реализована в программе схемотехнического моделирования в виде функционального модуля, представленного на рисунке ниже.

Схема троичного дешифратора типа «код–позиция» была протестирована на работоспособность совместно с моделью троичного двухразрядного асинхронного счетчика, как это показано на рисунке ниже.

По результатам тестирования троичный дешифратор типа «код–позиция» продемонстрировал вполне корректную и бессбойную работу.

Дешифраторы большей разрядности могут быть построены по тем же самым принципам: декодирование каждого троичного разряда в тройку битов согласно входным логическим уровням «0», «+1», «–1», и выборка необходимых совпадений в каждой строке таблицы истинности. Причем выборка может осуществляться двоичными логическими элементами.

Троичные декодеры типа «код–позиция» в микропроцессорной системе могут осуществлять дешифрацию адресного пространства системы, и способны к управлению специфическими газоразрядными индикаторами с позиционной системой отображения информации.

Наиболее известными среди них являются знаковые индикаторы, каждый из которых состоит из десяти тонких металлических электродов (катодов), каждый из которых соответствует одной цифре или знаку, и при этом они включаются индивидуально.

Пример такого индикатора приведен на рисунке ниже.

Электроды сложены так, что различные цифры появляются на разных глубинах, в отличие от плоского отображения, в котором все цифры находятся на одной плоскости по отношению к зрителю. Трубка наполнена инертным газом неоном (или другими смесями газов). Когда между анодом и катодом прикладывается электрический потенциал от 120 до 180 вольт постоянного тока, вблизи катода возникает свечение, соответствующее отображаемому знаку.

Индикаторы такого типа являются устаревшими, но их модели нередко встречаются в программных пакетах САПР и в программах схемотехнического моделирования.

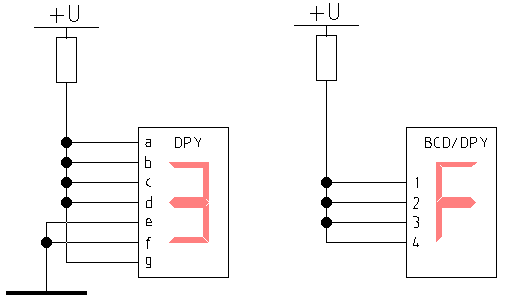

К сожалению, в используемой программе схемотехнического моделирования не оказалось индикатора подобного типа, но в наборе моделей имелись семисегментный индикатор с посегментным управлением (ниже на рисунке справа) и семисегментный индикатор с встроенным дешифратором двоичного позиционного кода «8–4–2–1» (слева).

Для визуализации троичного кода в разрабатываемых устройствах возникла необходимость разработать шифратор позиционного кода в двоичный позиционный код «8–4–2–1», поскольку схемотехника подобных шифраторов обычно проще.

Собственно, перекодировщики в цифровых системах обычно и выполняют по схеме «декодер–кодер», а поскольку рабочая модель троичного декодера типа «код–позиция» была успешно апробирована, кодер в двоичный позиционный код «8–4–2–1» был выполнен по принципу диодного шифратора, как это иллюстрирует рисунок ниже.

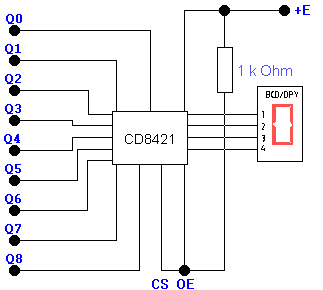

Подробности реализации кодера в двоичный позиционный код «8–4–2–1» прямого отношения к устройствам троичной логики не имеют, и стоит лишь здесь отметить, что он был выполнен в программе схемотехнического моделирования в виде функционального модуля, представленного на рисунке ниже.

Модель кодера позиционного кода в двоичный позиционный код «8–4–2–1» была апробирована под управлением троичного дешифратора типа «код–позиция» совместно с моделью троичного двухразрядного асинхронного счетчика, как это показано на рисунке ниже.

Результаты апробирования кодера позиционного кода в двоичный позиционный код «8–4–2–1» были признаны вполне успешными.

Следует лишь отметить, что все представленные модели рассчитываются в программе схемотехнического моделирования как аналоговые схемы, что позволяет увидеть особенности переходных процессов при переключении троичных логических устройств, но весьма замедляет процесс моделирования сложных схем даже на современных быстродействующих компьютерах.

Тем не менее, устройства, работа которых хорошо изучена на основе их аналоговых моделей, могут быть выполнены в дальнейшем в виде цифровых моделей, учитывающих лишь логические уровни, а также задержки переключения и распространения сигнала, в программных пакетах САПР, способных обрабатывать трёхуровневые логические сигналы.

Все упомянутые в тексте модели устройств

можно скачать здесь:

http://sgu-wap.narod.ru/Ternary/Download